1、 電磁兼容性(EMC)注意事項

EMC與電磁能量的生成、傳輸和接收有關,此電磁能量可能會擾亂電子系統的工作。來源(發射方)產生輻射,然後一個傳輸或耦合路徑會將輻射能量傳輸至接收方,即對輻射能量進行處理的地方,在此可引發良好或不良的行為。電子設備需要符合特定的限制,以滿足發出能源和易受外部事件的要求。世界各地的多個監管機構設定了地區性規格,以確保電子設備互不干擾。

CMOS模擬和數字電路具有很高的輸入阻抗。這導致它們對外部電場非常敏感。因此,您需要特別注意,以確保在輻射和導電噪聲存在的情況下,這些電路仍可以正常工作。

1、1 輻射干擾及輻射

輻射電能會影響系統的測量,並可能影響CapSense處理器內核的運作。在PCB板上,干擾會通過傳感器走線和其他數字和模擬輸入進入CapSense晶片。雖然CapSense提供了一個直觀和強大的接口,能夠通過消除機械部件提高產品的可靠性,它所產生的輻射發射(RE)又能加重電磁兼容性(EMC)問題。

請使用下面的技術來降低輻射干擾和發射。

1、1、1 通用EMI/EMC指南

1、1、1、1 接地層

一般的情況下,在PCB 板上正確放置接地層會降低RF 輻射和干擾。但是,接近CapSense 傳感器或用於將這些傳感器連接至PSoC 引腳的走線的實心接地層會增大傳感器的寄生電容。因此,推薦在傳感器周圍以及傳感器下方的PCB板底層上使用網格接地層,如接地層部分所介紹的內容。在PBC 板上的器件和其他電路部分下面的實心接地要遠離CapSense 傳感器和走線。不建議在CapSense 傳感器或走線10 mm 的範圍內使用實心接地層。多層電路板是首選。如果您使用四層或更多層的電路板,建議您將一層用作接地層,這對降低輻射很有幫助,因為它能大大減少接地層的抖動。

1、1、1、2 串聯電阻

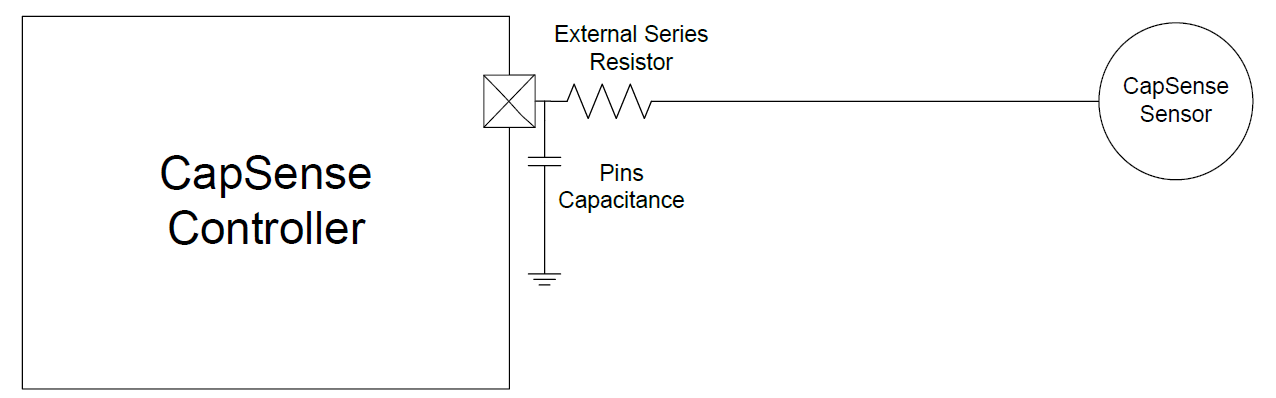

各個CapSense 控制器引腳均有各自的寄生電容(CP)。添加一個外部電阻可構成低通RC濾波器,從而減少耦合到引腳的RF 噪聲振幅。該電阻和連接到引腳的走線的寄生電容(如圖1-1 中所示的傳感器走線和傳感器墊塊)組合時,可構成能夠明顯降低RF 輻射的低通濾波器。因此,串聯電阻對於消除高次諧波和降低RF 干擾和輻射十分有用。

圖1-1. RC 濾波器

應將串聯電阻置於靠近PSoC 引腳的地方,以便能夠在PSoC 器件的輸入端過濾掉走線所引起的輻射噪聲。因此,推薦在PSoC 引腳的10 mm 內放置串聯電阻。

1、1、1、2、1 CapSense 輸入線路

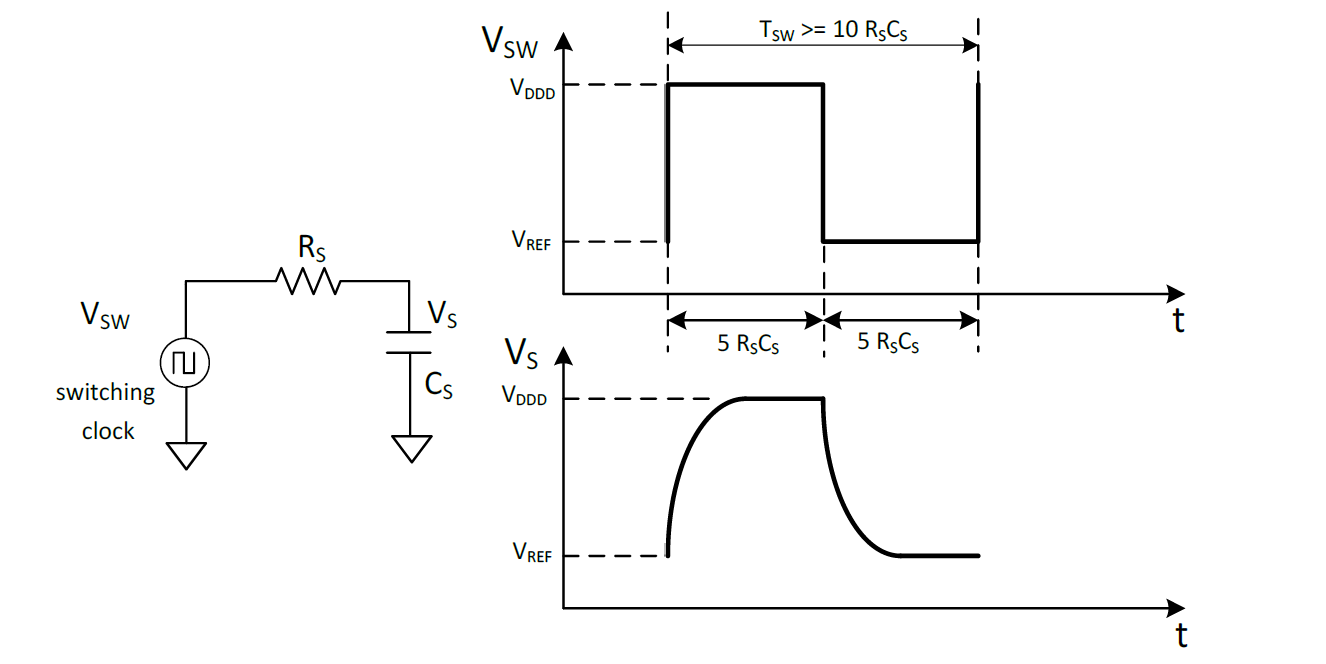

為了保證CapSense 正常工作,傳感器在每個開關周期中必須要滿充滿放。傳感器電容的充電和放電路徑本身具有的串聯電阻會減緩充電/放電過程。圖1-2 顯示了它的等效電路和產生的波形。增加電阻會改變將CP 轉化為等效電阻的開關電容電路的時間常數。如果串聯電阻值較高,開關電路的較低時間常數可抑制輻射和其干擾,但會限制可傳輸的電荷量。這樣不能實現對傳感器進行完全地充電和放電操作。這會降低信號等級,進而降低信噪比。電阻值越小越好,但在阻止射頻輻射和干擾方面卻不太有效。

通用覆銅PCB 上CapSense 輸入線路的串聯電阻推薦值為560 Ω。ITO 面板的電阻較大。電阻值選擇範圍僅為100 Ω至1 kΩ。串聯電阻通常使用的範圍為560 Ω 至4.7 kΩ,以實現EMC 目的。串聯電阻實際的最大值會因器件而異。其大小取決於多個因素,如:用作傳感器的GPIO 的電阻、用於掃描傳感器的開關頻率以及所需的信噪比。

圖1-2. 等效電路和波形

RS 是GPIO 電阻和外部串聯電阻的總和。CS 是傳感器的最大電容值。對於給定的開關頻率,必須選擇能夠對傳感器電容進行完全充電和放電的串聯電阻值。換句話說,對於給定的串聯電阻,必須選擇能夠對傳感器電容進行完全充電和放電的開關頻率值。如果不能修改其他CapSense 參數,那麼降低開關頻率會降低信噪比。因此,在串聯電阻值和開關頻率之間進行權衡,以實現所需性能。

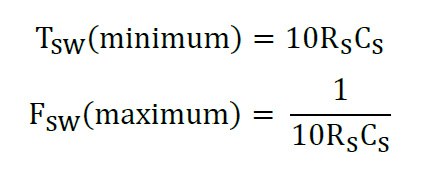

根據經驗,可選擇5RSCS 的周期用於充電和放電循環。用於計算最小值周期和最大頻率的公式分別為: 1、1、1、2、2 數字通信線路

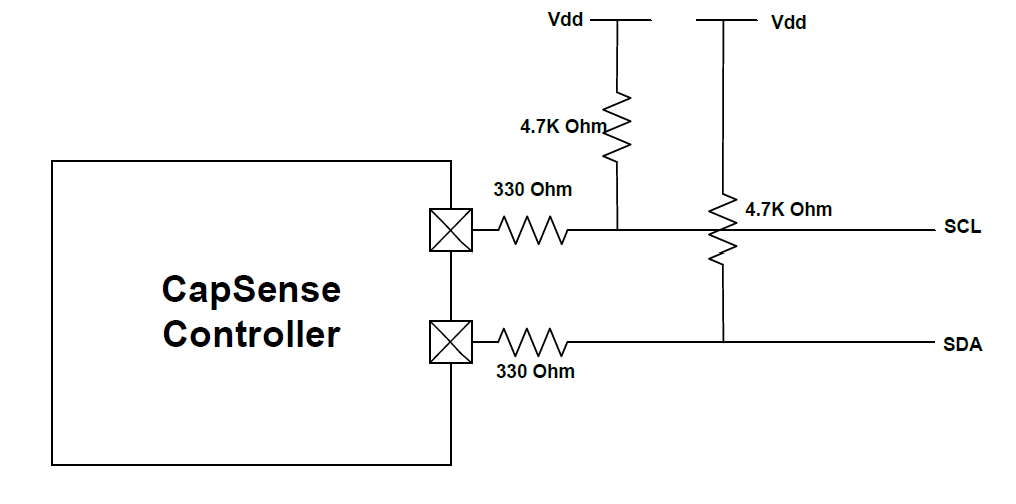

1、1、1、2、2 數字通信線路

通信線路,如I2C和SPI,同樣能受益於串聯電阻,並且推薦採用330 Ω。通信線路的走線一般較長,它們同CapSense走線一樣以天線的形式發射干擾。推薦在通信線路上採用一個大小為4.7 kΩ 的上拉電阻。因此,如果在這些線路上串聯超過330 Ω 的電阻,則電壓電平(VIL 和VIH)會超出規範範圍,在最壞的情況下還會使系統和接收器輸入阻抗間的供應電壓跌出規範範圍。由於當PSoC 輸出為低電平時,VIL 電平仍會保持為I2C 規範所要求的0.3 VDD,因此330 Ω 的電阻不會影響I2C 的操作。

圖1-3. 通信線路上的串聯電阻

1、1、1、3 走線長度

長走線比短走線引起的噪聲更多。長走線同樣會增加CP 值。所以要儘可能地縮短走線長度。

1、1、1、4 電流環路面積

另一個重要的布局注意事項是儘量縮短電流返迴路徑。接地層可降低全部接地阻抗,從而減少高頻率接地反彈。需要確保每個傳感器線路都具有良好的GND 返迴路徑。因為電流是在環路中流通的。除非高頻信號具有正確的返迴路徑,否則返回電流會通過較長的迴路路徑,從而形成較寬的環路;這樣會發生由互電感導致的信號問題。因此,會增大輻射和干擾。

如果器件封裝中包含了高頻電流環路,那麼能量也可以通過磁場耦合到器件外。通過磁通量可以使器件形成一個電流環路,以便鏈接到器件外面的電路環路。該互電感會在外部環路中產生一個意外電壓。同樣,外部的磁通量也會在內部電路環路中產生一個意外的電壓。通過使用儘可能小的電源和信號環路區域,可以最小化磁場耦合。在地面上拼接過孔(越多越好)。這樣會降低接地總阻抗。用於時鐘和振盪器電路等高頻率走線應同時連接到兩個接地線路。這樣可確保不會發生耦合情況(該情況會導致串擾)。如果可能,請使用獨立的接地層和電源層。圖1-4 顯示了一個不合理的接地方案示例。通過減少環路面積大大改善了布局。

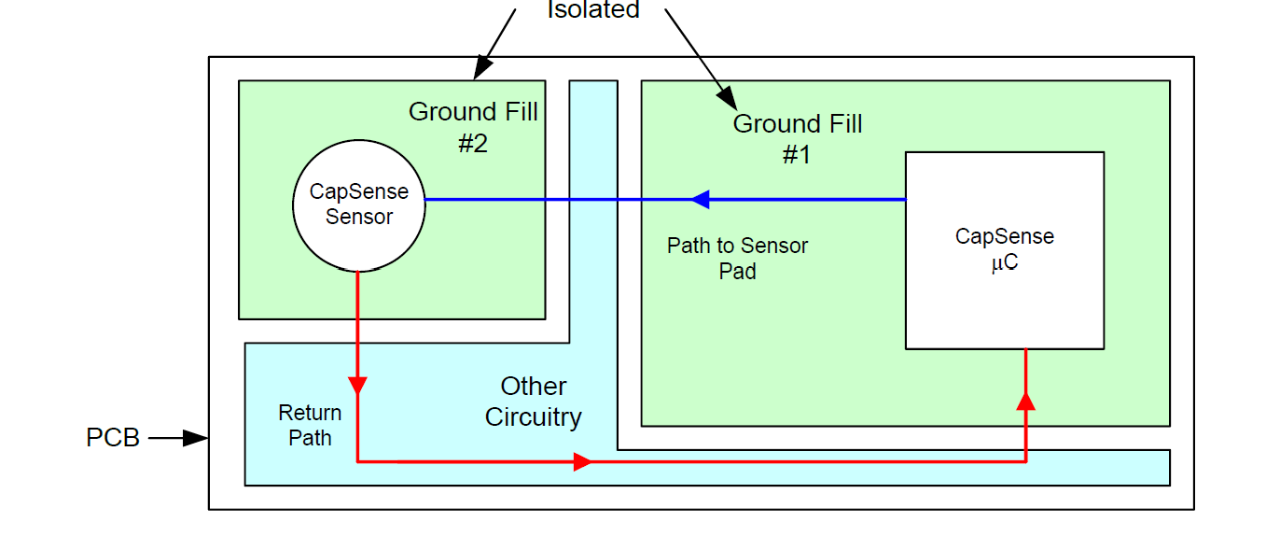

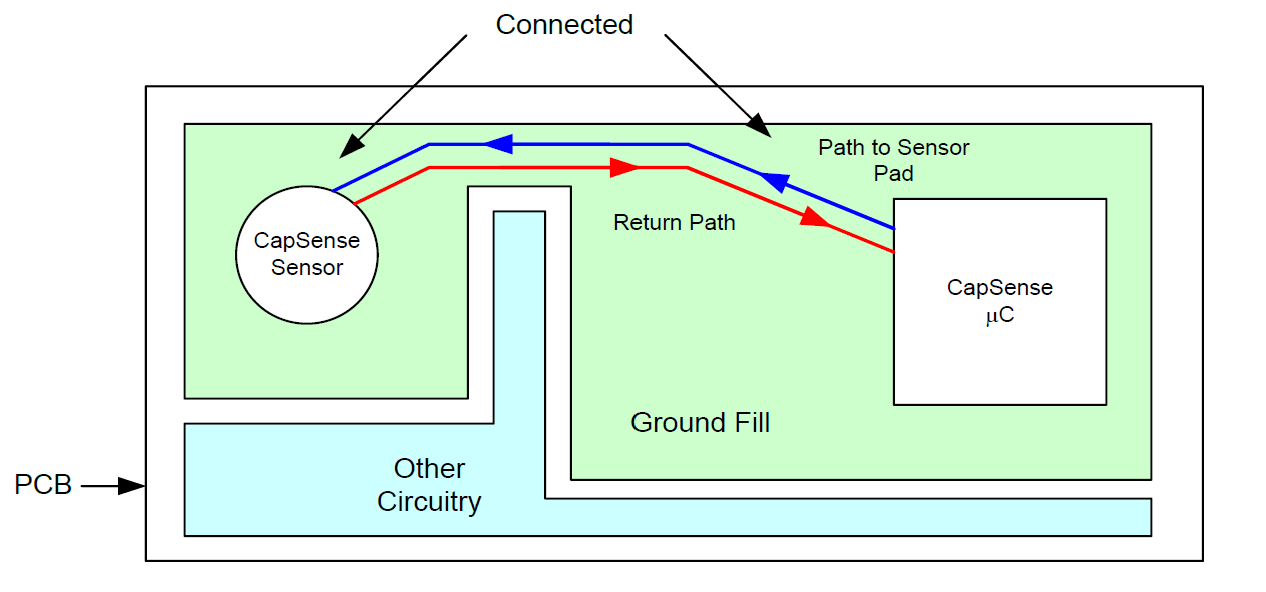

圖1-4. 不合理的接地方案和接地環路

在圖1-5 中,一個接地層圍繞著兩個傳感器,此接地層與CapSense 控制器接地連接,而接地層圍繞著第三個傳感器。第三個傳感器通過其他電路的長線被連接到其他接地層,從而造成電流環路。在這種布局下,第三個傳感器會更容易受輻射噪聲影響,且會增加輻射。在原理圖上這兩個接地部分位置相同,所以更好地布局的話它們可能是一個連接的區域。

圖1-5. 不合理的電流環路布局

圖1-6 說明了前面示例中的合理布局。通過連接兩個接地區域,減少了環路面積。

圖1-6. 合理的電流環路布局

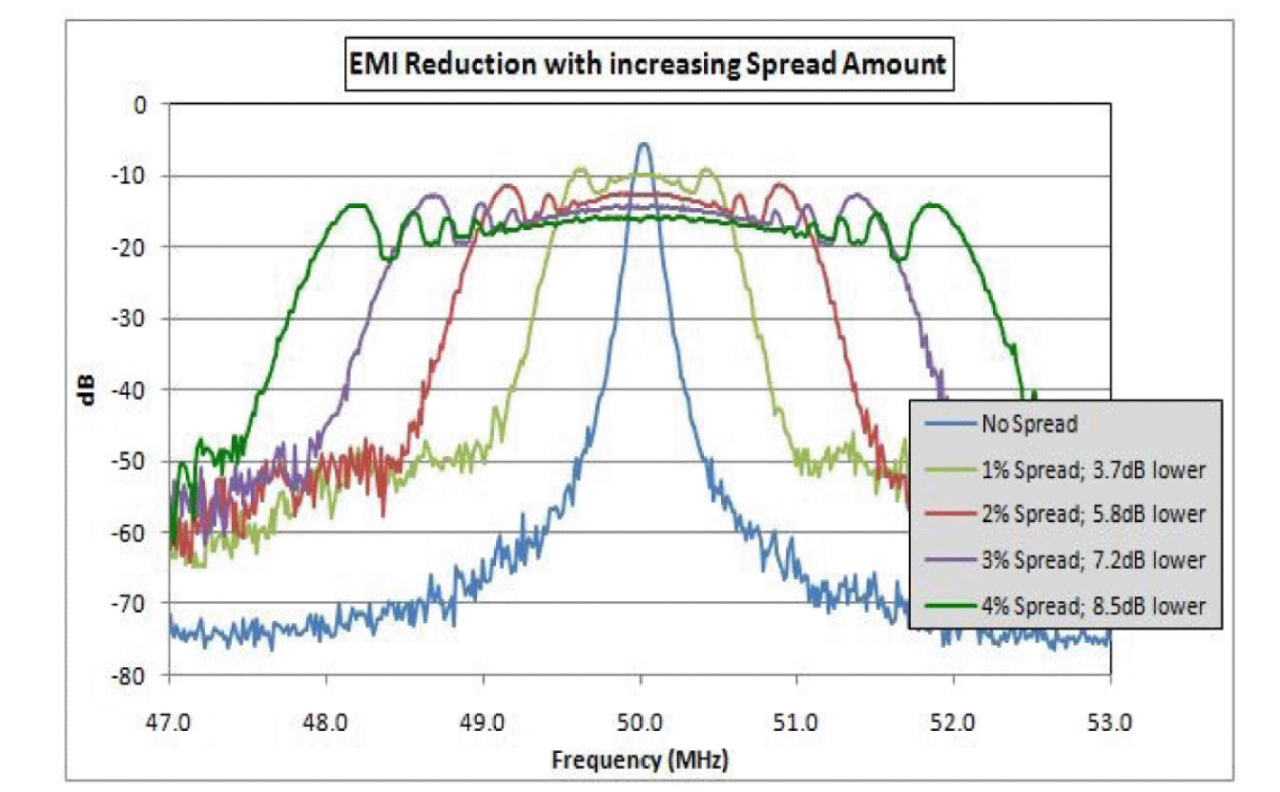

1、1、1、5跳頻

跳頻是一種通過較窄的頻帶擴展輸入信號或工作頻率的方法。該方法有助於降低峰值,並實現在頻率範圍內(如圖1-7 所示)擴展輻射和干擾。下面介紹了PSoC 的各種跳頻方法:

圖1-7. 跳頻

掃描傳感器時實現IMO抖動:可以對不同的傳感器進行IMO抖動或調整操作。例如,當基本IMO頻率為24 MHz時,那麼使用24 MHz到22 MHz的頻率範圍對IMO頻率進行掃描。只能使用一個頻率對傳感器進行掃描。使用不同的頻率對不同的傳感器進行掃描。這樣,通過擴展輻射可降低峰值。

進行掃描時可實現IMO抖動:還可以在每次進行掃描實現IMO抖動。當一個傳感器被掃描時,那麼使用24 MHz到22 MHz的頻率範圍對IMO頻率進行掃描。因此,該方法可防止使用一個頻率對傳感器進行掃描。這樣,通過擴展輻射可降低峰值。該方法還可以提高抗RF干擾的能力。

擴頻時鐘(SSC):通過使用外部時鐘也能夠使PSoC工作。與實現IMO抖動方法相同,使用擴頻時鐘也有助於在較寬的頻率範圍內擴展輻射。在PSoC1內,只能使用埠P1[4]提供外部時鐘。在這種情況下,必須將引腳P1[4]驅動模式設置為數字高阻態。這有助於提高抗RF干擾的能力和擴展輻射。

偽隨機序列(PRS):使用PRS(並不是固定的時鐘源)可以降低CapSense引腳上的噪聲(通過減少由固定頻率源引起的EMI),並提高對其他頻率源和它們諧波的抗EMI能力。這有助於提高抗RF干擾的能力和擴展輻射。