本範例使用 MIMXRT1020-EVK 搭配 NXP 原廠提供 Hardware Development Guide 來說明上電時續的硬體配置

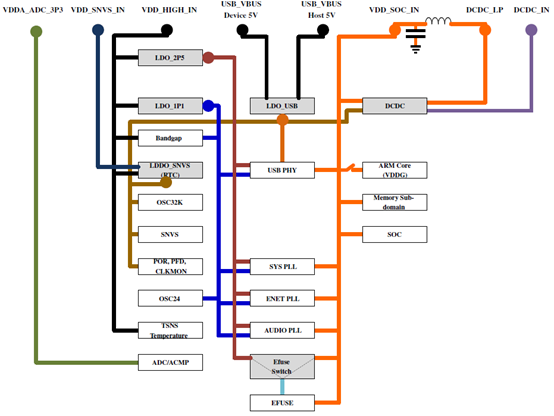

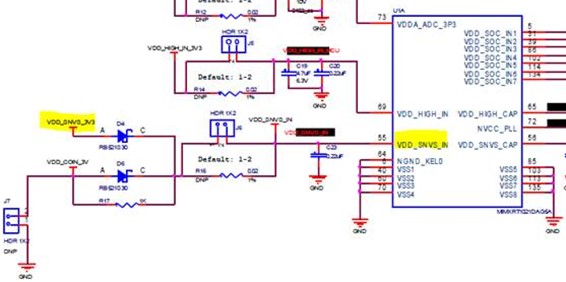

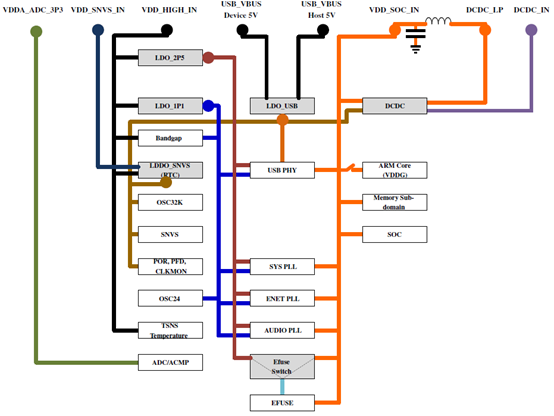

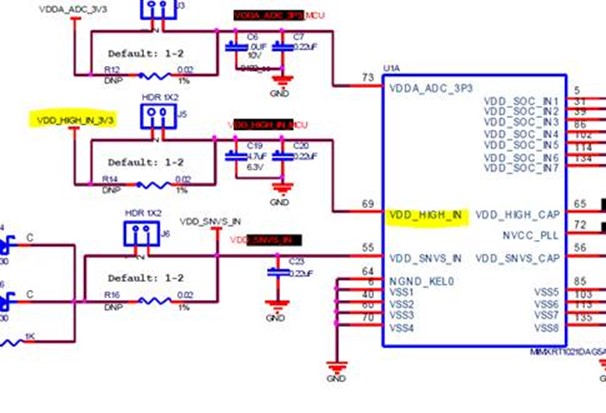

RT1020 內部有多組 LDO分別對 MCU 各部原件供電 ( 如圖 1 ) 因此有上電時續要求

圖 1

圖 1

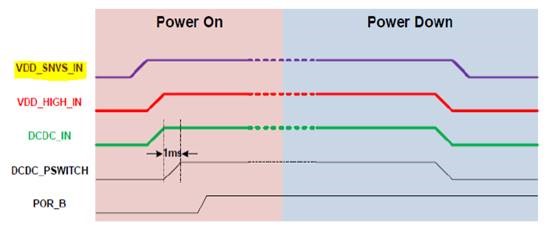

對應原廠提供 Hardware Development Guide for the MIMXRT1020 Processor 中的 Figure 1 ( 如圖 2 )

圖 2

圖 2

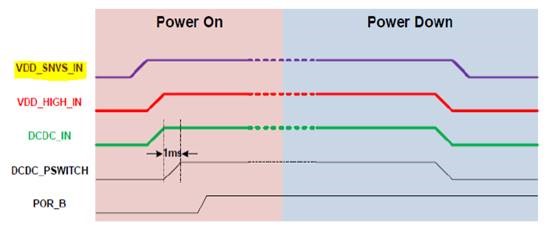

而原廠 MIMXRT1020-EVK 規劃 Power sequence 方式如下:

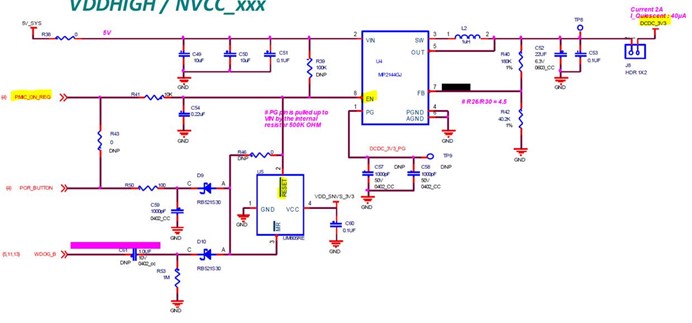

圖 3

圖 3

圖 4

圖 4

圖 5

圖 7

圖 7

圖 8

圖 8

圖 9

圖 10

圖 10

圖 11

圖 12

圖 13

圖 14

圖 14

圖 15

圖 15

原廠 MIMXRT1020-EVK 藉由上述 7 個 Step 元件配置來完成上電時續。

參考資料來源:

[1] Hardware Development Guide for the MIMXRT1020 Processor

[2] i.MX RT1020 Processor Reference Manual

[3] i.MX RT1020 Crossover Processors for Industrial Products

[4] SPF-29856_B1 ( MIMXRT1020-EVK SCH )

RT1020 內部有多組 LDO分別對 MCU 各部原件供電 ( 如圖 1 ) 因此有上電時續要求

圖 1

圖 1對應原廠提供 Hardware Development Guide for the MIMXRT1020 Processor 中的 Figure 1 ( 如圖 2 )

圖 2

圖 2而原廠 MIMXRT1020-EVK 規劃 Power sequence 方式如下:

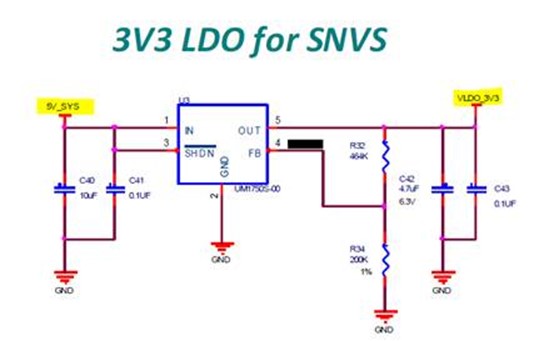

Step 1 :

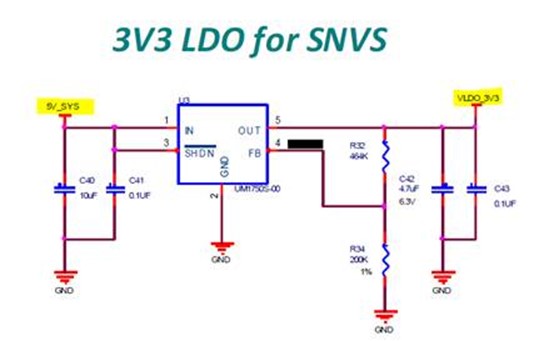

透過外部電源 5V_SYS 給 VLDO_3V3_IN 並輸出 VLDO_3V3 ( 如圖 3 )

圖 3

圖 3Step 2 :

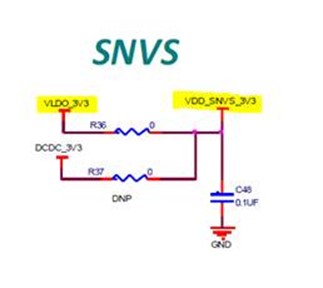

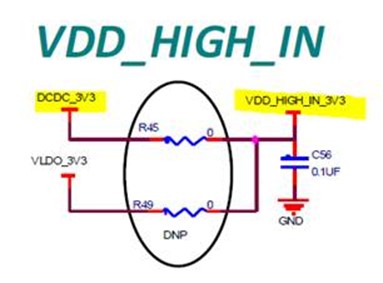

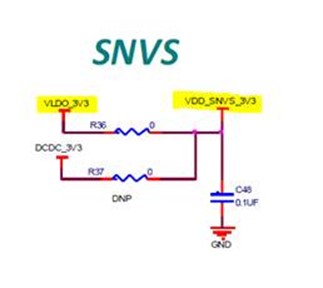

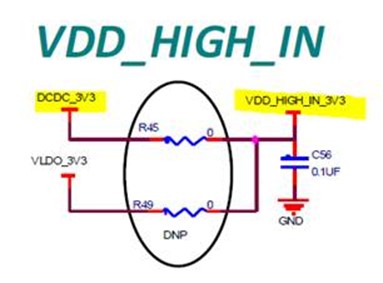

VLDO_3V3 透過 0 歐姆電阻配置到 VDD_SNVS_3V3,

先讓 MCU 內部 SNVS 上電 ( 如圖 4、5 )

先讓 MCU 內部 SNVS 上電 ( 如圖 4、5 )

圖 4

圖 4

圖 5

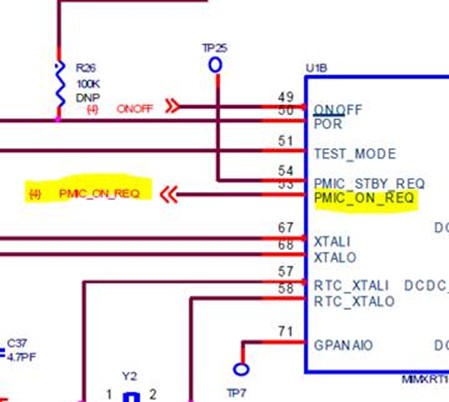

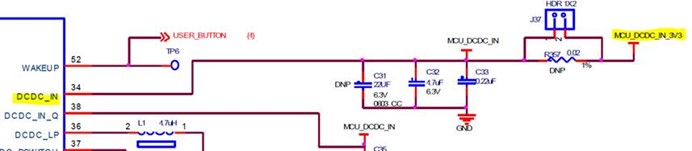

Step 3 :

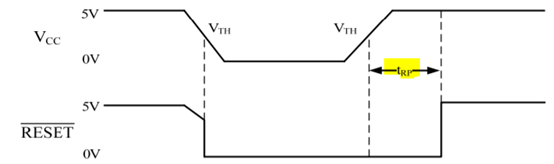

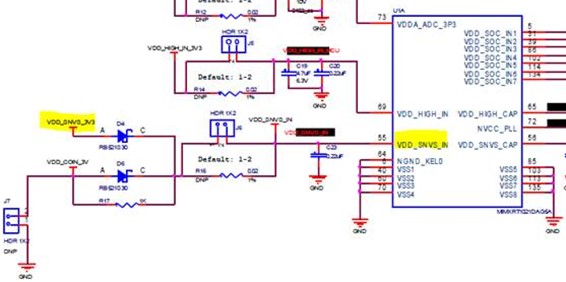

MCU 內部 LDO_SNVS 穩定後,MCU 的 PMIC_ON_REQ Pin 將會輸出 High 準位電壓 ( 如圖 6 )

圖 7

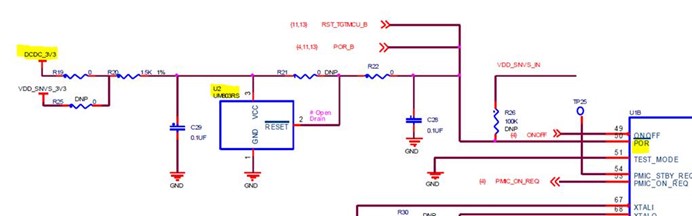

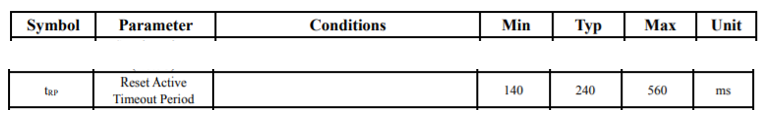

圖 7Step 4 :

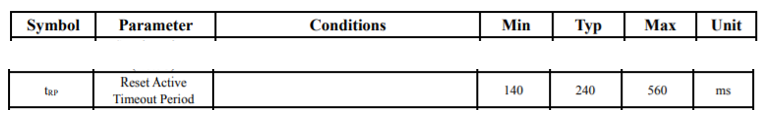

PMIC_ON_REQ Pin 上拉 UM805RE_RESET Pin ( Open Drain ),

此時 UM805RE 將會產生至少 140 ms 的時序,而後對 MP2144GJ EN Pin 供電 ( 如圖 8、9 )

此時 UM805RE 將會產生至少 140 ms 的時序,而後對 MP2144GJ EN Pin 供電 ( 如圖 8、9 )

圖 8

圖 8

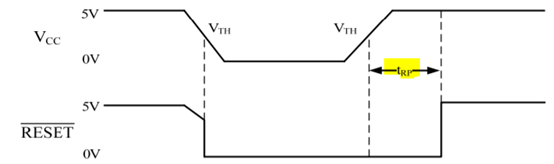

圖 9

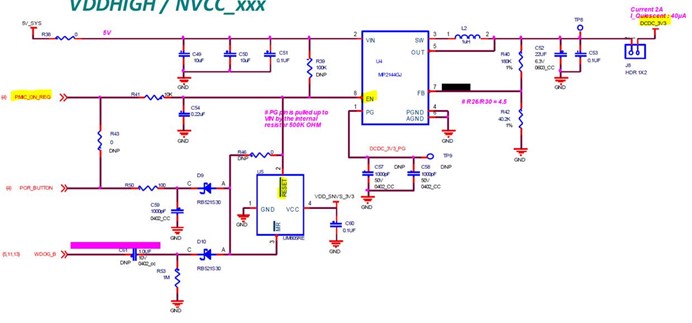

Step 5 :

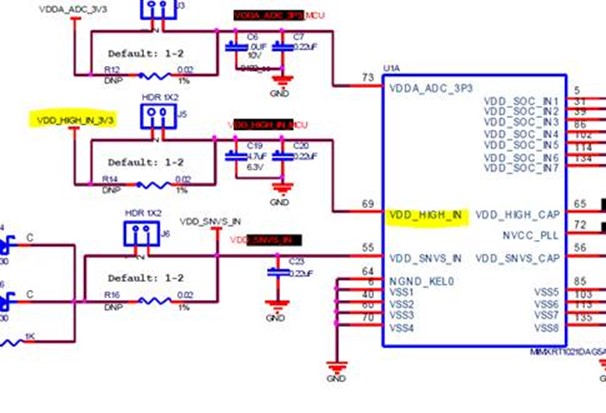

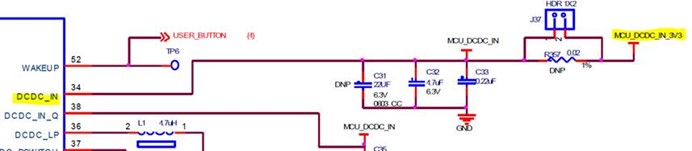

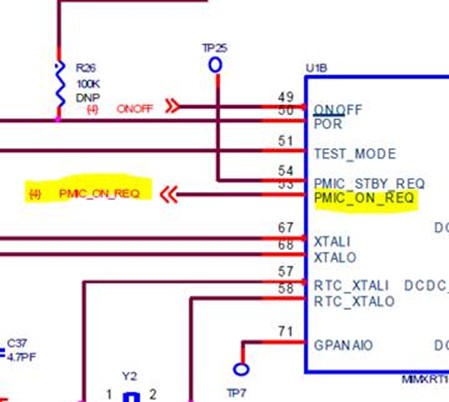

由 MP2144GJ 產生 DCDC_3V3 對 MCU VDD_HIGH_IN、DCDC_IN 供電 ( 如圖 10 ~ 13 )

圖 10

圖 10

圖 11

圖 12

圖 13

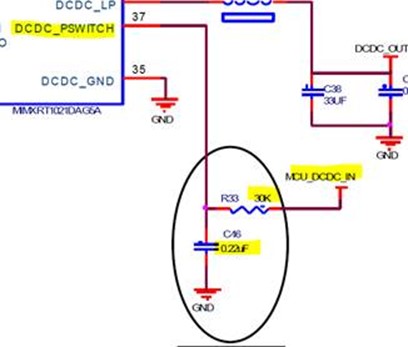

Step 6 :

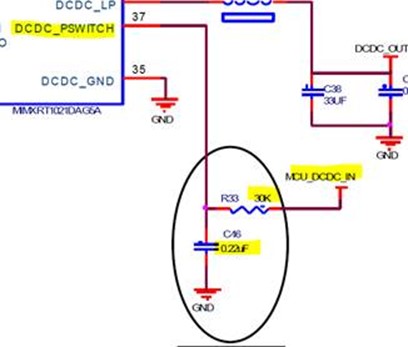

DCDC_PSWITCH 部分則由 RC 電路配置 30 K歐姆電阻與 0.22 uF 電容,

產生 6.6 ms 時序 ( 如圖 14 )

產生 6.6 ms 時序 ( 如圖 14 )

圖 14

圖 14Step 7 :

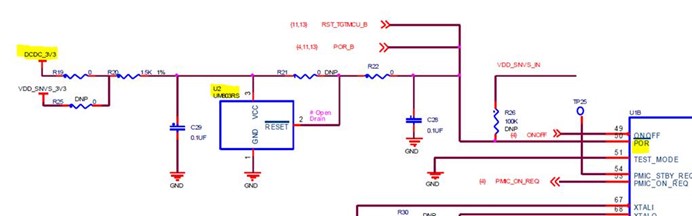

POR_B 部分則由 UM805RS_Reset IC 來完成上電時續,

由 DCDC_3V3 上拉 UM805RS_RESET Pin ( Open Drain ),

此時 UM805RS 將會產生至少 140 ms 的時序,而後對 POR_B 供電,

達成對 MCU 進行 Reset 功能 ( 如圖 15 )

由 DCDC_3V3 上拉 UM805RS_RESET Pin ( Open Drain ),

此時 UM805RS 將會產生至少 140 ms 的時序,而後對 POR_B 供電,

達成對 MCU 進行 Reset 功能 ( 如圖 15 )

圖 15

圖 15原廠 MIMXRT1020-EVK 藉由上述 7 個 Step 元件配置來完成上電時續。

參考資料來源:

[1] Hardware Development Guide for the MIMXRT1020 Processor

[2] i.MX RT1020 Processor Reference Manual

[3] i.MX RT1020 Crossover Processors for Industrial Products

[4] SPF-29856_B1 ( MIMXRT1020-EVK SCH )