CADS 是 Customer Application Demo Software 的簡稱,經由 S32DS 編譯,通過 OpenSDA 或者是 SWD 即可燒錄進 S32K144。如此一來,便可以在運行時通過 PC 終端程序(如 Tera Term)輸入已經定義好的命令,實現 NJJ29C2 相關配置。

所以 CADS 可以在 NJJ29C2 硬體設計完成之後對硬體檢驗,如 SPI 通訊是否正常,天線設計是否失諧以及天線設計有無短路等等。

同時 CADS 的 “SPILOG_CONFIG(1);”命令還可以將 SPI 通訊可視化,用戶可以清晰直觀地看見整個流程中的命令幀和響應幀(如果配置正確的話)。

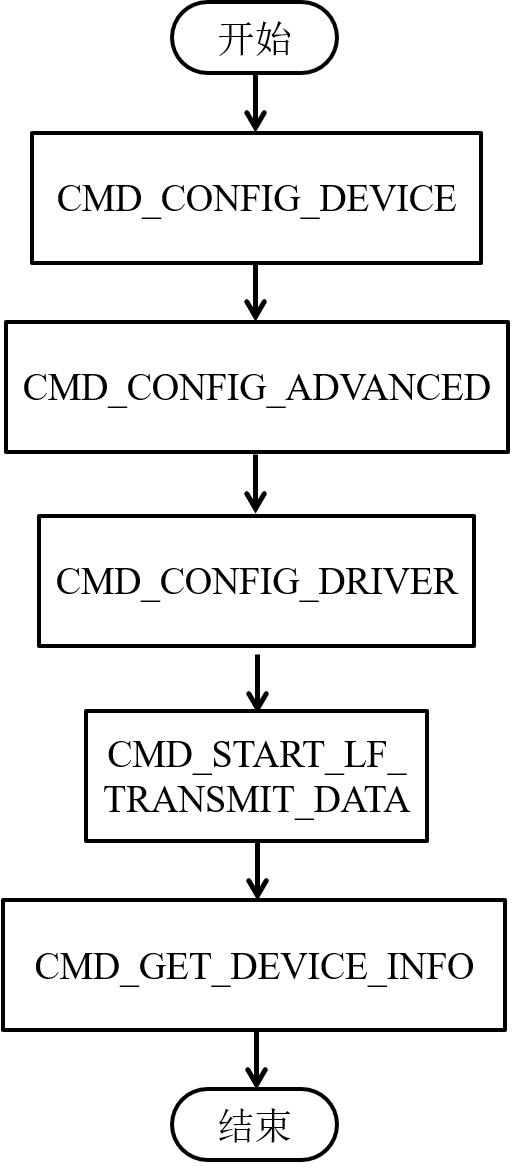

以 Impedance Learning 為例,CADS 的 SPI 命令配置流程(不包含 CADS 自身定義的函數命令)如 圖 1.1 所示。

圖 1.1 CADS Impedance Learning 配置流程圖

在發送了 CMD_CONFIG_DEVICE 等一系列命令,進行參數設定之後,通過 PKE 發送由 continuous wave(CW)LF segments 組成的 LF frame sets(注意不能包含曼切斯特編碼的 LF data 或者是半位寬編碼)。這樣在 LF frame sets 發送結束時,就會對天線阻抗、相位以及電流等天線參數進行更新。對於 LF frame set 以及 LF segment 的介紹可以參考 附錄 1。

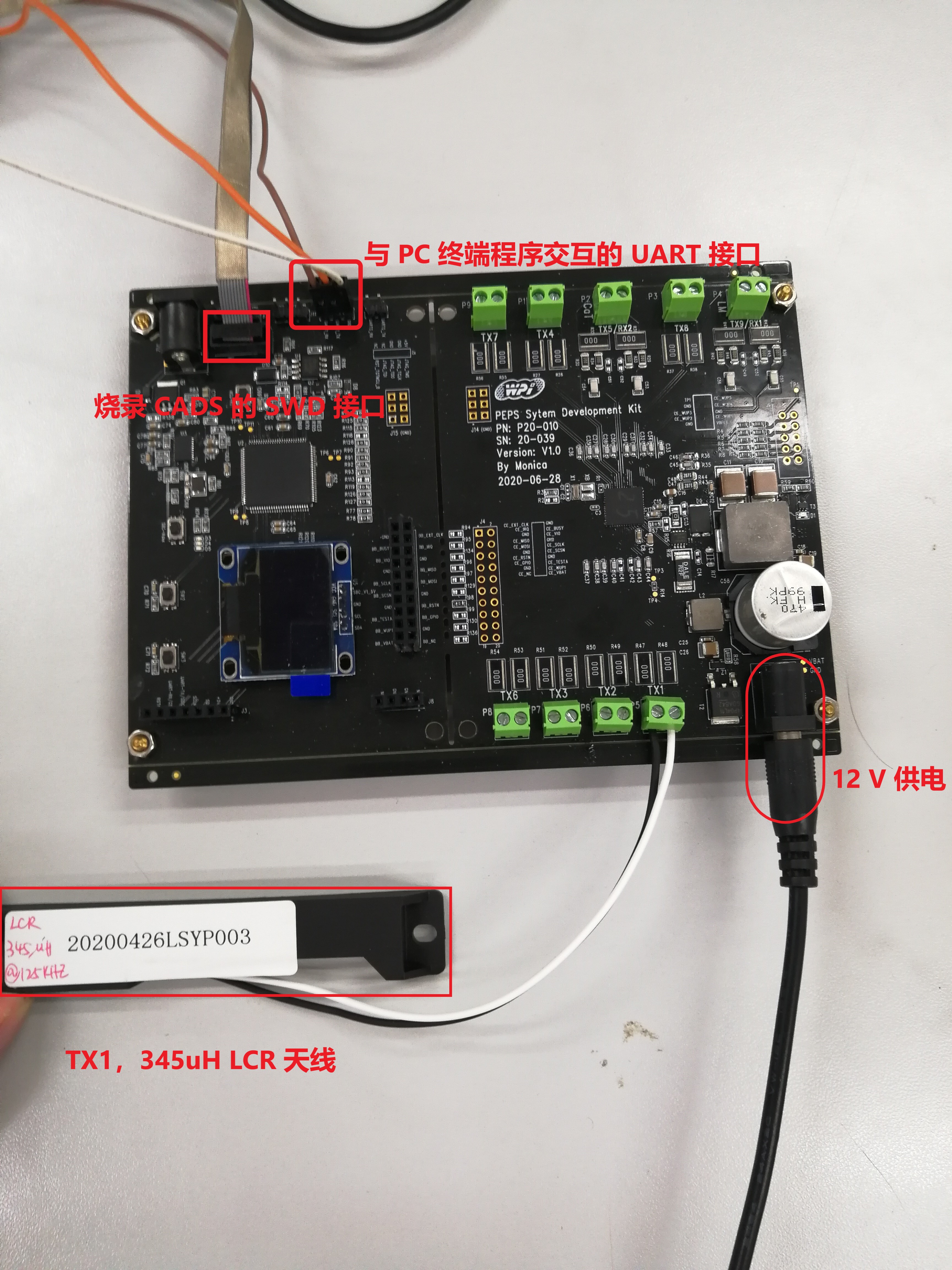

緊接著,只需要通過 CMD_GET_DEVICE_INFO 檢索 device 響應,就可以選擇性獲取上一個 PKE 或 IMMO 詳細的操作信息和診斷信息。這些信息中就包含了 RESP_DIAG 提供的被激活天線的 LF driver 電流、相位以及阻抗的測量結果。圖 1.2 是測試 CADS 的硬體環境搭建(不包含高頻接收 NCK2910)。

圖 1.2 CADS 硬體環境搭建

圖 1.3 為 VDR 及 LF driver 信息診斷報告,其中由於只有 TX1 連接了天線,所以它的阻抗、相位及電流等信息得到了更新。另外如果驅動回報的天線電流為 0mA,那麼也可以說明該位置天線處於開路。

|

(DBG) DIAG response (DBG) VDRMEASMIN: 14.6 V (DBG) VDRMEASMAX: 14.6 V (DBG) DR1_ZEFF: 11.50 Ohm (DBG) DR1_PHASE: 35.85 degree (DBG) DR1_CURRENT: 512.50 mA (DBG) DR2_ZEFF: 21.00 Ohm (DBG) DR2_PHASE: 0.00 degree (DBG) DR2_CURRENT: 0.00 mA (DBG) DR3_ZEFF: 21.00 Ohm (DBG) DR3_PHASE: 0.00 degree (DBG) DR3_CURRENT: 0.00 mA (DBG) DR4_ZEFF: 21.00 Ohm (DBG) DR4_PHASE: 0.00 degree (DBG) DR4_CURRENT: 0.00 mA (DBG) DR5_ZEFF: 21.00 Ohm (DBG) DR5_PHASE: 0.00 degree (DBG) DR5_CURRENT: 0.00 mA (DBG) DR6_ZEFF: 21.00 Ohm (DBG) DR6_PHASE: 0.00 degree (DBG) DR6_CURRENT: 0.00 mA (DBG) DR7_ZEFF: 21.00 Ohm (DBG) DR7_PHASE: 0.00 degree (DBG) DR7_CURRENT: 0.00 mA (DBG) DR8_ZEFF: 21.00 Ohm (DBG) DR8_PHASE: 0.00 degree (DBG) DR8_CURRENT: 0.00 mA (DBG) DR9_ZEFF: 21.00 Ohm (DBG) DR9_PHASE: 0.00 degree (DBG) DR9_CURRENT: 0.00 mA |

圖 1.3 VDR & LF driver 特性測量報告

二、 程式說明在 NJJ29C2 復位完成之後,終端程序會顯示如下內容,由於 WPI 並沒有 Lizard(NCK2910)的硬體設備,所以它會顯示“Fail in Initialization Lizard”的字樣:

|

(INF) ============== CENDRIC CADS (v3.4) ==============

(INF) Supported commands for each IMMO protocol: (INF) HT-Pro2: GET_IDE, GET_IDE64, AUTHENT, INIT_AC, MUTE (INF) HT-AES: START_AUTH (INF) X-Tag-Pro2 : INIT_CT, GET_IDE, GET_IDE64, PING, BROADCAST, USER (INF) HT-3: None

(INF) Check initial CENDRIC response (ERR) Operation mode: ERROR (ERR) Reset info: (ERR) RST_RSTN reset is active (CMD) v3.0> (INF) Initialization Lizard starts (ERR) Fail in Initialization Lizard (CMD) v3.0> (INF) RAM image does not exist (INF) Init script does not exist (CMD) v3.0> |

當出現上述提示(NCK2910 初始化失敗的信息可以忽略,因為就算沒有 NCK2910,CADS 也可以繼續執行大部分命令),也就可以通過鍵入、複製粘貼或者是文件拖放的方式將 X21_Learn_TX1.txt 中 SPI 命令輸入到 PC 終端程序,然後再通過 UART 被 S32K144(內含 CADS)接收解析,進而對 NJJ29C2 進行配置。

對於 NJJ29C2 的初始化配置,可以說就是一套基本算得上固定的流程,其中涉及到 3 個主要的 SPI 命令:CMD_CONFIG_DEVICE、CMD_CONFIG_ADVANCED 以及 CMD_CONFIG_DRIVER,與這些命令相關的參數構成、參數配置的詳細信息請參考 NXP 的 NJJ29C2 Objective User Manual。本篇文章僅是針對 WPI PEPS System Development Kit 硬體情況進行參數配置。關於上述 3 個命令的參數設定及簡單說明如下:

|

/* CMD_CONFIG_DEVICE 中設定 T_TXCHG = 128us,LF driver Baud rate = 4kbps, 選擇了 DR1 和 DR2 的高功率模式(HPDR),VDRMAX = 35V,VDRMIN = 15V, I_COILMAX_INIT = 16A,I_COILMAX_OP = 16A*/ (CMD) v3.0> CMD_CONFIG_DEVICE(1,0x08,0x02,0x04,0x40,0x21,0x01,0xD5,0xFF,0x10,0 x00,0x00,0x00,0x01,0xFF,0xFF,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00);

(INF) Command name: CMD_CONFIG_DEVICE (INF) Command parameters: 0x01, 0x08, 0x02, 0x04, 0x40, 0x21, 0x01, 0xD5, 0xFF , 0x10, 0x00, 0x00, 0x00, 0x01, 0xFF, 0xFF, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00

/* CMD_CONFIG_ADVANCED 這個參數配置可以說是固定的,它能將 LF Driver 的 占空比設定成接近 40% 的目標值 */ (CMD) v3.0> CMD_CONFIG_ADVANCED(1,0x03,0xBB,0xB3,0xE5,0x15,0xF2);

(INF) Command name: CMD_CONFIG_ADVANCED (INF) Command parameters: 0x01, 0x03, 0xBB, 0xB3, 0xE5, 0x15, 0xF2

/* CMD_CONFIG_DRIVER 選擇了 DR1,設定初始阻抗為 10Ω(這裡要設置為期望的 最小阻抗。如果實際的阻抗比該值還小,很有可能導致實際電流比目標值高,存在 風險),設定初始天線感量 345uH,設定最大相位容差 ±67.5°, 最大容許電流容差 ±18.75%, 最小天線阻抗容差 10Ω,最大 60Ω */ (CMD) v3.0> CMD_CONFIG_DRIVER(1,0x01,0x02,0x28,0x44,0xED,0x28,0xF0);

(INF) Command name: CMD_CONFIG_DRIVER (INF) Command parameters: 0x01, 0x01, 0x02, 0x28, 0x44, 0xED, 0x28, 0xF0 (CMD) v3.0> CMD_START_LF_TRANSMIT_DATA(1,0x04,0x01,0x28,0x04,0x05); |

通過 CMD_START_LF_TRANSMIT_DATA 發送 continuous wave(未調節),在阻抗等信息更新之後,使用 CMD_GET_DEVICE_INFO 檢索 RESP_DIAG 的結果,完成 Impedance Learning,具體的配置及說明如下:

|

/* CMD_START_LF_TRANSMIT_DATA 設定 1 個 frame set 的長度為 4 個字節, 選擇工作的通道為 DR1,天線目標電流為 1.25A(HPDR), 數據段編碼方式則是未經過調整的 CW,持續時間 384us */ (CMD) v3.0> CMD_START_LF_TRANSMIT_DATA(1,0x04,0x01,0x28,0x04,0x05); WAIT_IRQ(50);

(INF) Command name: CMD_START_LF_TRANSMITRESP_PARSING_CONFIG(2); _DATA (INF) Command parameters: 0x01, 0x04, 0x01, 0x28, 0x04, 0x05 (CMD) v3.0> (INF) Command name: WAIT_IRQ (INF) Command parameters: 0x32 (CMD) v3.0> (DBG) INFO: (DBG) LF activity is finished

/* CMD_GET_DEVICE_INFO 檢索 RESP_DIAG */ (CMD) v3.0> CMD_GET_DEVICE_INFO(0,2); RESP_PARSING_CONFIG(1);

(INF) Command name: RESP_PARSING_CONFIG (INF) GPIO name: (INF) Command parameters: 2 (INF) Configuration succeeded! (CMD) v3.0> (INF) Command name: CMD_GET_DEVICE_INFO (INF) Command parameters: 0x00, 0x02 (CMD) v3.0> (DBG) DIAG response (DBG) VDRMEASMIN: 14.6 V (DBG) VDRMEASMAX: 14.6 V (DBG) DR1_ZEFF: 11.50 Ohm (DBG) DR1_PHASE: 35.85 degree (DBG) DR1_CURRENT: 512.50 mA (DBG) DR2_ZEFF: 21.00 Ohm (DBG) DR2_PHASE: 0.00 degree (DBG) DR2_CURRENT: 0.00 mA (DBG) DR3_ZEFF: 21.00 Ohm (DBG) DR3_PHASE: 0.00 degree (DBG) DR3_CURRENT: 0.00 mA (DBG) DR4_ZEFF: 21.00 Ohm (DBG) DR4_PHASE: 0.00 degree (DBG) DR4_CURRENT: 0.00 mA (DBG) DR5_ZEFF: 21.00 Ohm (DBG) DR5_PHASE: 0.00 degree (DBG) DR5_CURRENT: 0.00 mA (DBG) DR6_ZEFF: 21.00 Ohm (DBG) DR6_PHASE: 0.00 degree (DBG) DR6_CURRENT: 0.00 mA (DBG) DR7_ZEFF: 21.00 Ohm (DBG) DR7_PHASE: 0.00 degree (DBG) DR7_CURRENT: 0.00 mA (DBG) DR8_ZEFF: 21.00 Ohm (DBG) DR8_PHASE: 0.00 degree (DBG) DR8_CURRENT: 0.00 mA (DBG) DR9_ZEFF: 21.00 Ohm (DBG) DR9_PHASE: 0.00 degree (DBG) DR9_CURRENT: 0.00 mA (CMD) v3.0> (INF) Command name: RESP_PARSING_CONFIG (INF) GPIO name: (INF) Command parameters: 1 (INF) Configuration succeeded! (CMD) v3.0> |

三、 參考資料

- Um525831 – NJJ29C2 Objective User Manual (Rev. 3.1, 19 June 2020)

- UM – SCA1903 – NJJ29C2 Customer Demo Operation (Rev. 3.0, 8 May 2020)

- NJJ29C2 Explanations about initializations of application examples (Rev. 1.0, 15 July 2020)

四、 附錄

LF segment 是 LF telegram 的最小實體,包含了數據編碼方式以及對應的數據。LF frame set 則是由一個或多個 LF segments 再加上 LF drivers 配置所組成的。要區分 LF frame set 其實非常簡單,因為它是以 Length,也就是 LFFRAMELEN,作為起始的。在 LF frame set 與 LF frame set 之間,會存在傳輸變換時間(可以通過 CMD_CONFIG_DEVICE 設置)。

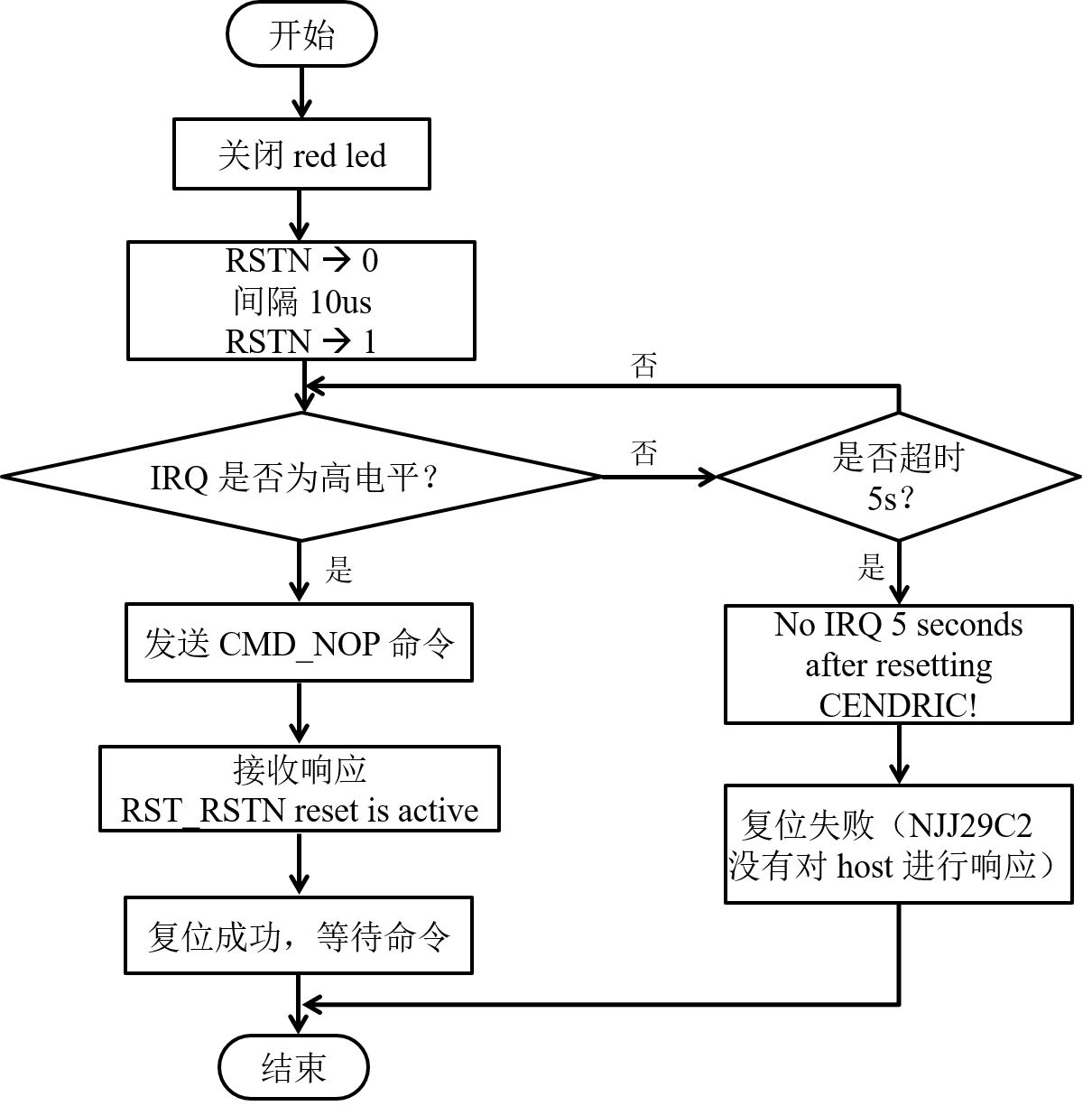

最初調試 WPI 板子的時候,終端程序會提示“(INF) No IRQ 5 seconds after resetting CENDRIC!”,告知 S32K144 對於 NJJ29C2 的初始化失敗。通過對 CADS 程序進行分析,可以整理出初始化流程如 圖 4.1 所示:

圖 4.1 初始化配置流程

出現上述問題我首先檢查了 NJJ29C2 供電 VBAT 以及 VIO 均處於正常範圍,然後也檢查了 SPI 通訊接口,SCSN、SCLK、SDI、SDO 均沒有問題。然後結合 圖 4.1 的流程來分析,發現 S32K144 是會控制 GPIO 對 NJJ29C2 的 RSTN 引腳進行復位操作的,如果 RSTN 並沒有拉低,RESP_GENERIC 中的 POR 內的 RST_RSTN 就不會為 1。具體表現就是 NJJ29C2 對於 S32K144 的操作沒有響應,IRQ 電平也不會拉高。5s 之後就會提示“No IRQ 5 seconds after resetting CENDRIC!”。

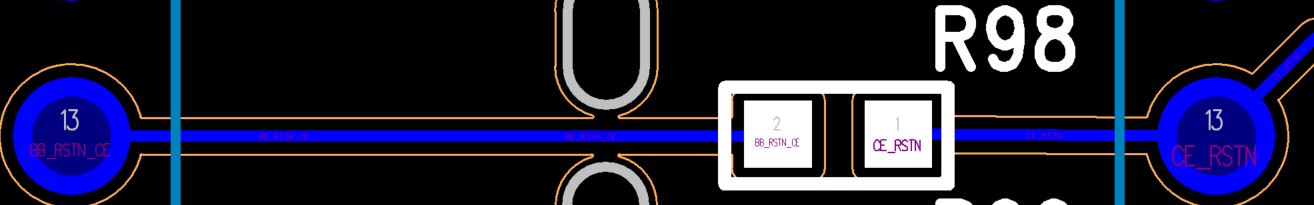

檢查之前的 PCB,發現 Base Board 與 LF Board 之間 RSTN 連線是斷開的,而 R98 也並沒有貼上 0Ω 電阻,當貼上電阻之後,問題得到解決。問題根源如 圖 4.3 所示:

評論