最新版本的雙倍資料速率(DDR) DRAM規格與前一代相較有許多演進,也為打造記憶體元件的設計工程師們帶來新的可能性──甚至還有一些奇怪的挑戰。

由產業標準組織JEDEC Solid State Technology Association在今年稍早公佈的ESD79-5 DDR5 SDRAM標準,是為了滿足從客戶端系統到高性能伺服器的廣泛應用,在省電性能方面持續增加的需求所設計;特別是後者正面臨密集的雲端與企業資料中心應用越來越高的性能壓力。整體來看,與DDR4相較,DDR5規格可提供開發者兩倍的性能與大幅改善的省電效率。

更具體來說,DDR5規格的目標是改善大規模應用的性能,同時在較高速度下的通道效率也不打折扣;這是透過將突發長度(burst length,BL)加倍至BL 16,以及將記憶體庫數量(bank-count)從16增加至32。JEDEC形容將DDR 5架構形容為「革命」,提供更高的通道效率與更高的應用級性能,將可實現下一代運算系統的持續演進。為了可靠性與效率的提升,DDR5 DIMM在同一個模組上具備兩個完全獨立的40位元子通道。

不過市場研究機構Objective Analysis首席分析師Jim Handy表示,儘管比起DDR4有大幅度的演進,對設計工程師來說,DDR5並不意味著徹頭徹尾的變化。「從第一代DDR到現在,參考設計被所有的電路板佈線應用,記憶體子系統的每一個部分都必須通過驗證;」包括從連接器到DIMM的所有東西,「當設計工程師拿到手都會是經過驗證的,所以DDR4與DDR5從設計的角度來看實在沒有差別。」

他補充指出,並不是很多工程師需要在兩者之間做選擇;「決策權在於處理器製造商。」某款處理器可能要求採用DDR4,其他則是DDR5。除了處理器架構之外,需要做選擇的只有自己設計FPGA與ASIC的人,但是「那些設計採用DRAM的不多。」

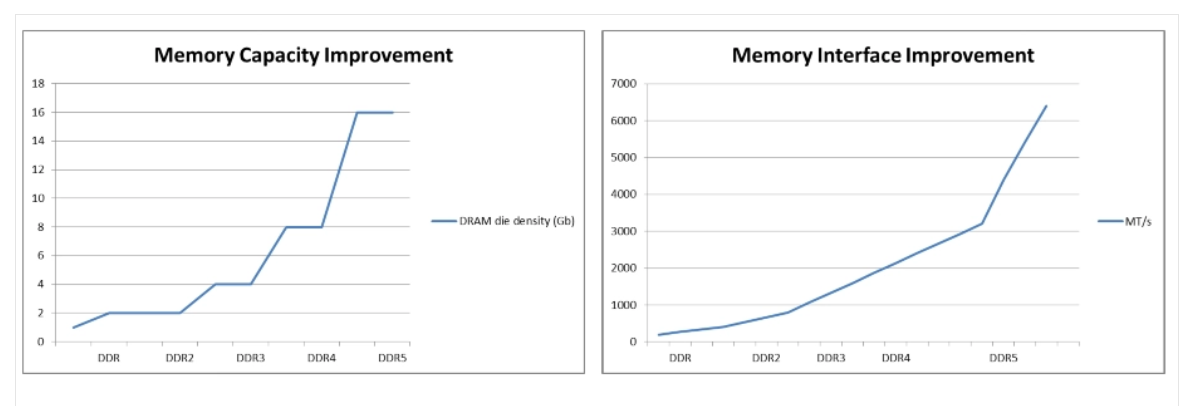

Handy表示,DDR5最亮眼的部分就是速度比已經「夭壽快」的DDR4還要快。

(圖片來源:JEDEC)

DRAM大廠美光(Micron)首席架構師Frank Ross認為,前進DDR5沒什麼挑戰,不過電壓調節從系統轉移到DIMM需要花一點時間習慣;「對我們來說在DIMM有電壓調節是一大優勢,可以簡化主機板並改善電力傳輸網路。」

Ross指出,DDR4與DDR5之間的差異所帶來的挑戰不足為懼,「每一次我們遇到這種更快的速度,特別是我們正在尋找的DDR5這種速度,新的挑戰會是確保訊號傳輸良好,而且是包括系統設計與主機板設計;」將會有大量新的訓練演算法需要開發,「所有人都要調整。」

他表示,所需的訓練提醒了我們,只是將DRAM的速度一代代加倍,牽涉的工作很多,但是所有這些工作實現了DDR5的演進,並確保新規格能在未來順利長期發展,這也是可靠性非常重要的原因。DDR5一開始的容量密度是16Gb,最終將達到32Gb,中間可能會有一個24Gb的過渡;「這對我們來說很重要,因為該規格將存在很長一段時間,得確保我們能解決DRAM繼續微縮的問題,因此我們真的不得不非常密切關注可靠性。」

在某應用案例情境中,可靠性至關重要──支援企業級私有雲與公有雲的資料中心對DRAM需求龐大,並將持續快速成長,預期會是第一波更新至DDR5的應用。Ross表示,「我們得確保我們提供大規模運作的可靠性;」他指出,頻寬加倍只是性能提升的一小部份原因,更妥善利用匯流排效益,也對DDR5有利,「我們想維持資料匯流排的持續利用,」透過系統中更多的記憶體庫,DDR5能更新資料存取的併發操作,提供大幅超越DDR4的性能表現。

作者 : Gary Hilson,EE Times特約編輯

- 2020-12-10

編譯:Judith Cheng

(參考原文:DDR5 Brings Design Ops, Challenges,by Gary Hilson)

評論