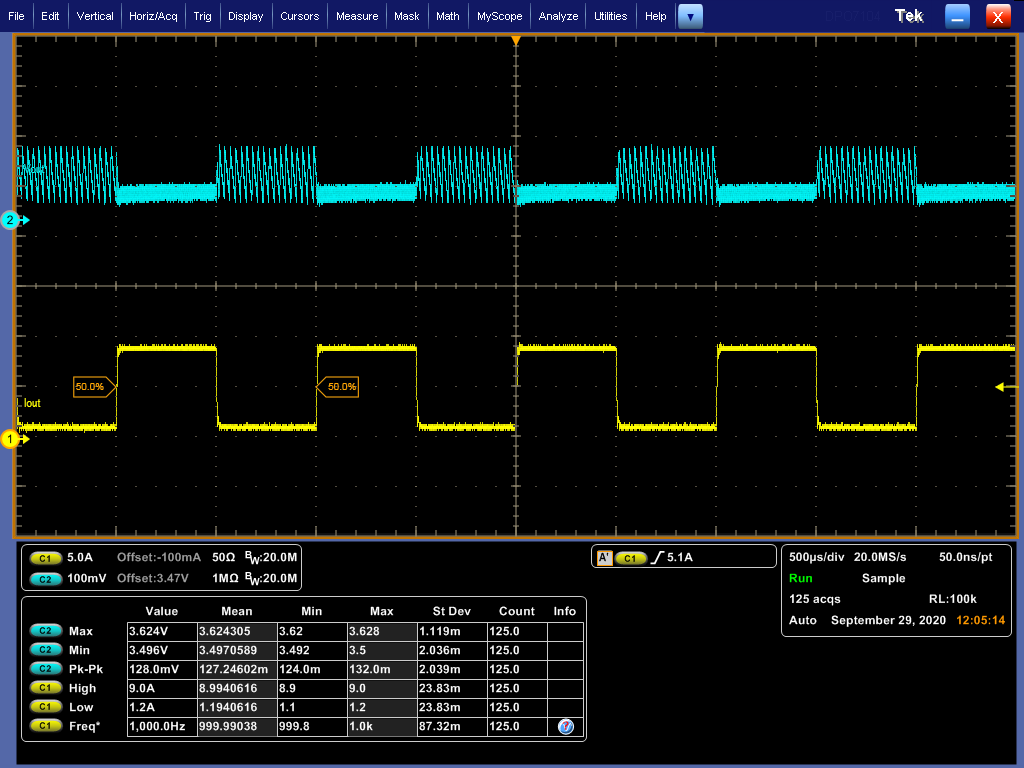

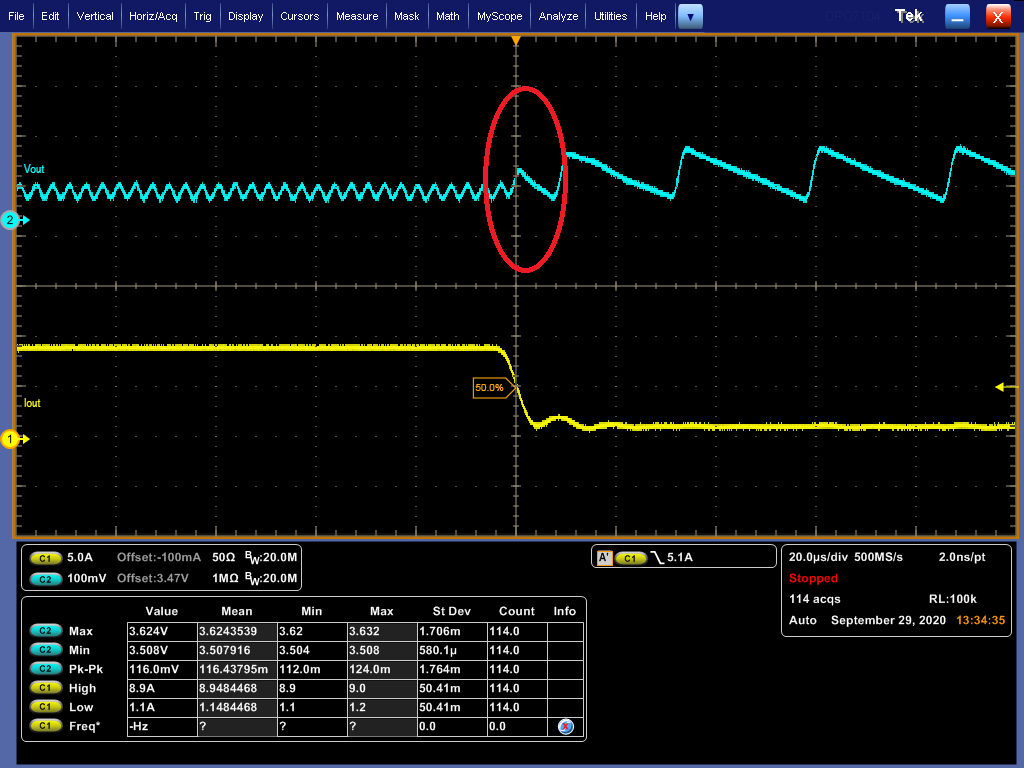

以下實測波形是以COT架構的controller所得的結果。

buck controller demo board 的condition 如下:

Vin=12, Vout=3.3

Load current condition: High current=9A, Low current=1A, FSW=1kHz, Slew rate=2.5A/uS

1張正常的load transient的波形應該如下:

使用最短路徑,bandwidth=20MHz

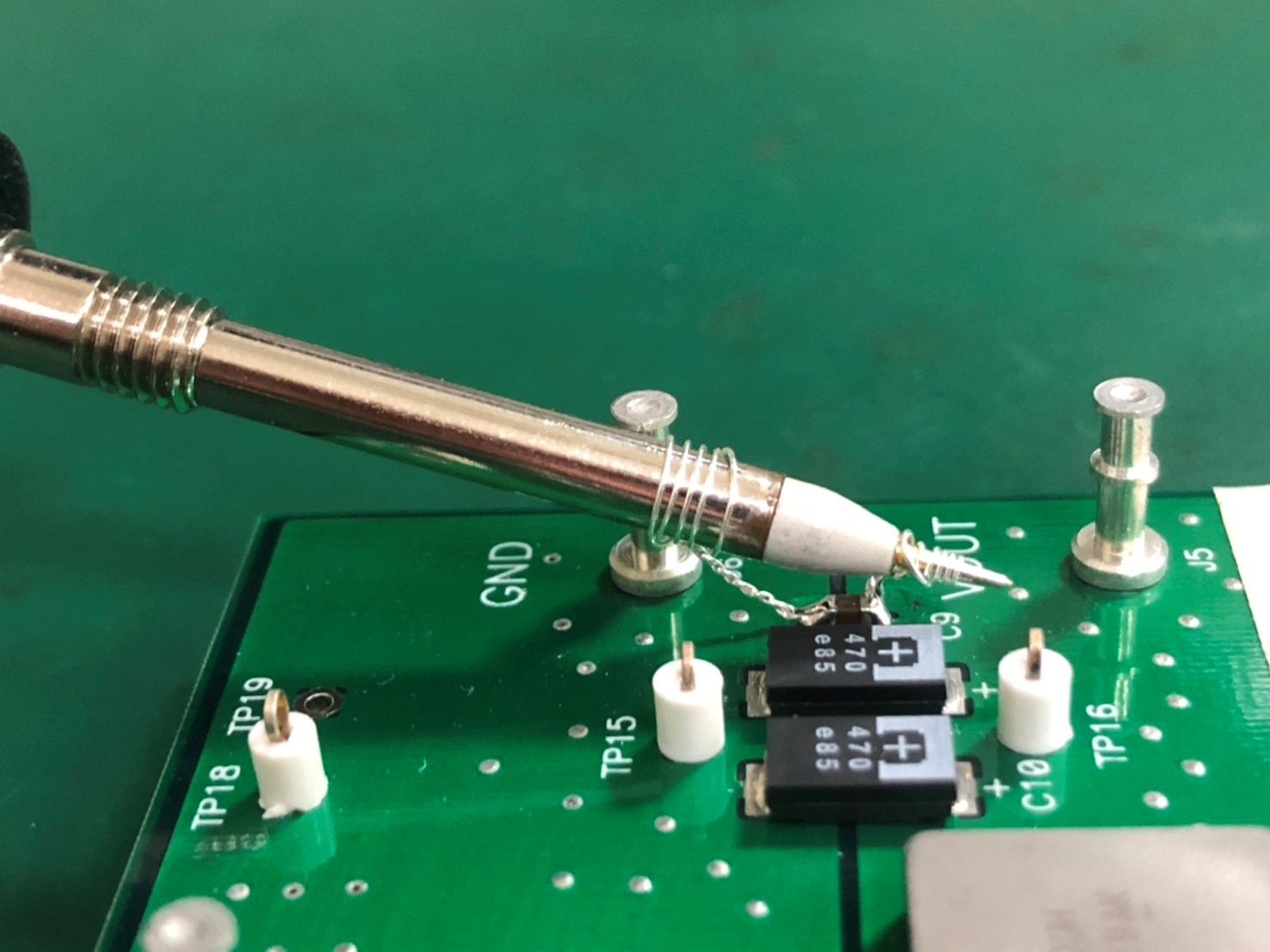

最短路徑

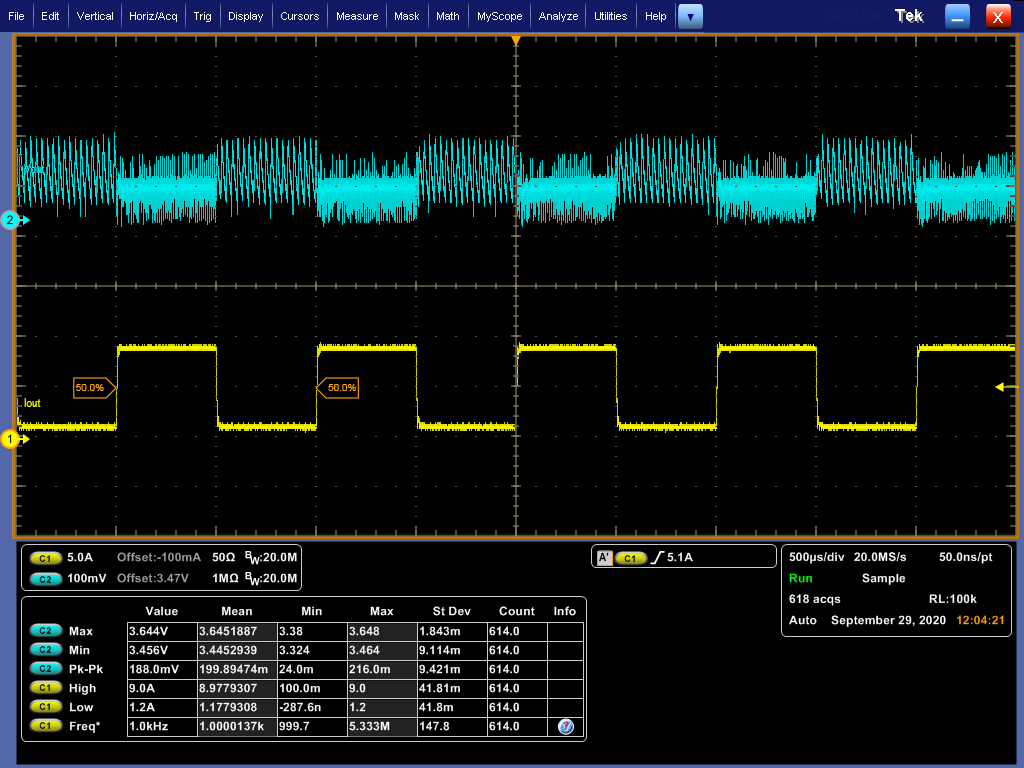

如果沒有使用最短路徑也會看到ripple受到switch信號的干擾如下圖

沒有使用最短路徑

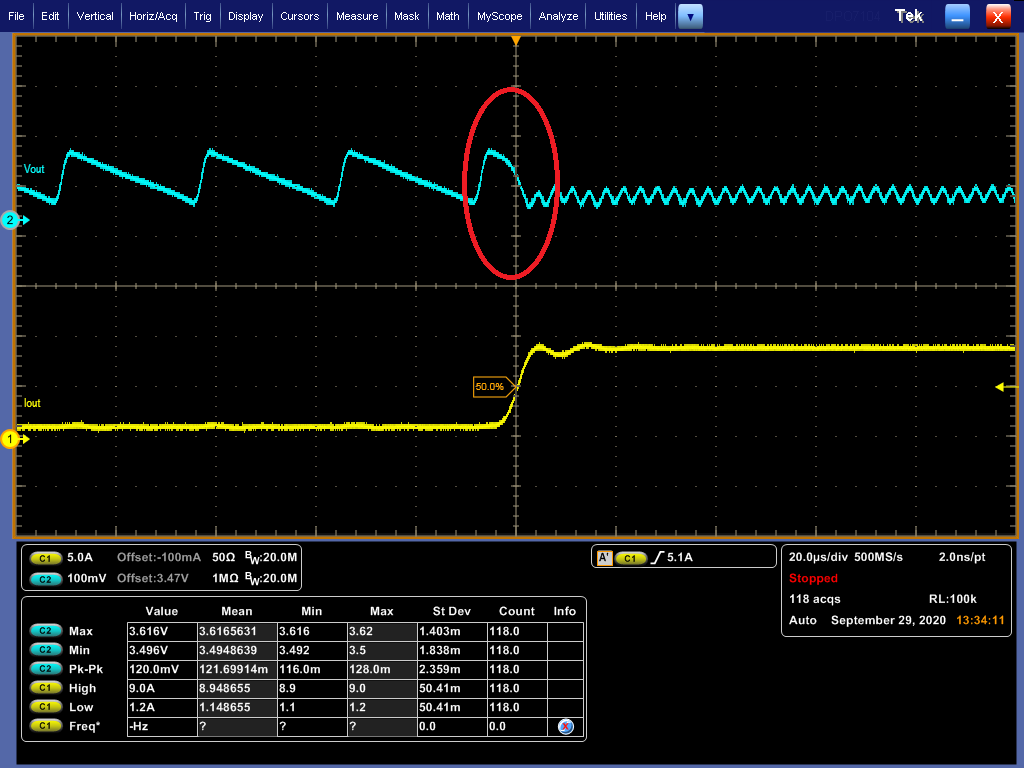

將time scale拉開來看,由於COT架構在反應速度的表現比較好所以在負載電流變化時,輸出電壓不會有太大的變動

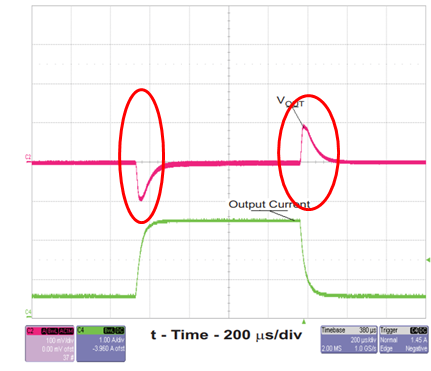

如果是量測需要調整補償的current mode或voltage mode而補償值又沒最佳化的話則可能得到以下波形

可以看到輸出電壓在負載電流變化時的變動比較大,如果要改善這個結果可以透過下列的方式:

- 如果有外部補償的腳位(COMP pin), 微調這腳位上的R、C值

- 如果沒有外部補償的腳位則可進行以下動作

- 增加輸出電容的容值

- 提高controller的工作頻率

- 減小電感的感值

評論