功能介绍:

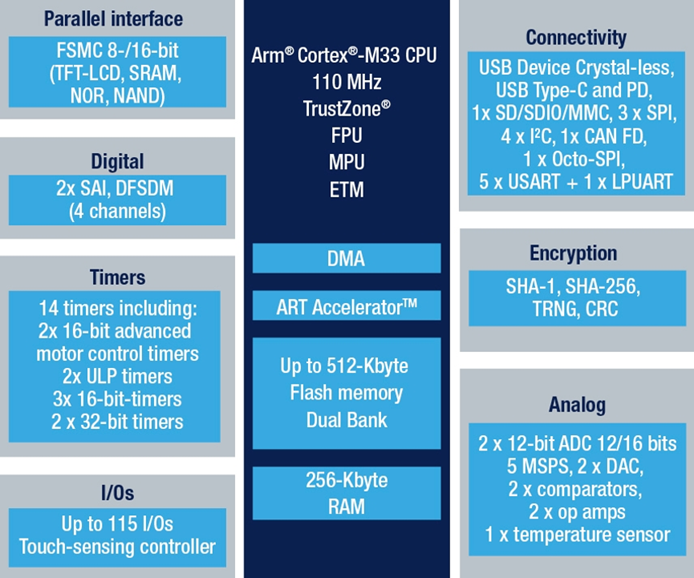

意法半導體推出IoT的MCU兼備超低功耗與資料安全的STM32L5微控制器。STM32L5系列MCU的時鐘頻率高達110MHz,基於整合Arm TrustZone®硬體安全技術的Arm® Cortex®-M33 32位RISC處理器內核。STM32L5系列MCU增加了更多加強版安全功能,包括靈活的軟體隔離、安全啟動、金鑰的儲存和硬體加密加速器。自我調整電壓調節、即時加速、功率門控和多種低功耗模式。STM32L5具有512 KB雙區快閃記憶體,允許讀寫同時操作,方便設備管理,並支援錯誤校正碼(ECC)診斷,提高資料安全性;並具備256KB SRAM,支援高速外部記憶體,包括單線、雙線、四線或八線SPI和Hyperbus 快閃記憶體或SRAM,提供SRAM、PSRAM、NOR、NAND或FRAM記憶體介面。

大大购相关商品 NUCLEO-L552ZE-Q >> 查询存货及售价

STM32L5的數位外設包括帶專用電源的USB 全速控制器,即使系統電源是1.8V,仍然可以使用USB傳輸資料,還包括符合USB Type-C 1.2版和USB Power Delivery 3.0版規範的UCPD控制器,兩個12 bitsADC、兩個DAC、兩個超低功耗比較器和兩個運算放大器,其中兩個運算放大器有外部或內部電壓跟隨電路和可程式設計增益放大器(PGA)功能。

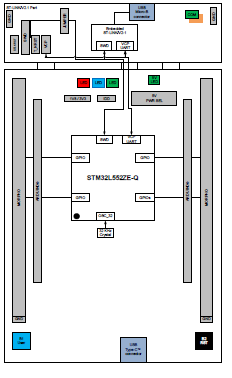

MCU內部方塊圖

NUCLEO-L552ZE-Q圖片

NUCLEO-L552ZE-Q方塊圖

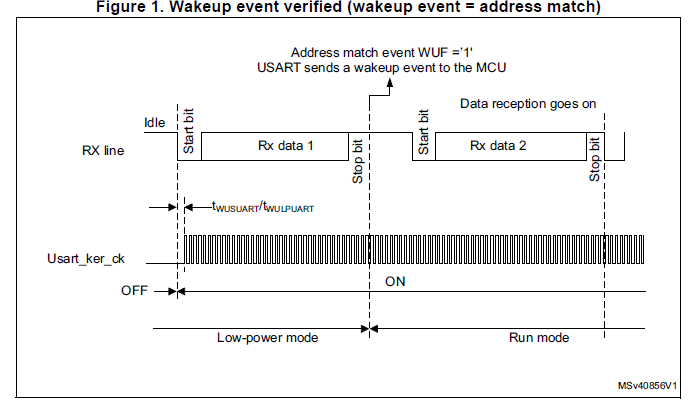

USART/LPUART喚醒功能

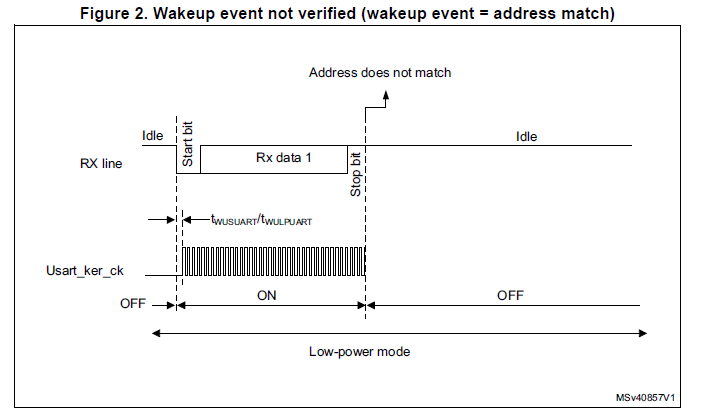

以下為STM32L5 以USART/LPUART喚醒的功能,MCU處於低功耗模式且用作USART/LPUART內核時鐘的HSI時鐘關閉,當在 USART/LPUART接收線路上檢測到下降沿時,USART/LPUART介面請求重新開啟HSI時鐘。然 後,將使用HSI時鐘進行幀接收。 如果喚醒事件得到驗證,將從低功耗模式喚醒MCU並進行正常的資料接收。 如果喚醒事件未得到驗證,HSI時鐘將重新關閉,MCU不喚醒並維持低功耗模式,內核時鐘 請求被釋放。圖 1和圖 2顯示了程式設計為“位址匹配檢測”的喚醒事件的範例。

圖一

圖二

倍頻域 僅當外設支持倍頻域時,USART/LPUART才能將MCU從低功耗模式喚醒。這意味著可通過獨 立於APB時鐘的時鐘為USART/LPUART提供時鐘。此時鐘可以是HSI或LSE時鐘。因此,即 使USART/LPUART時鐘被禁用且MCU處於低功耗模式,USART/LPUART也能夠接收資料。

USART/LPUART喚醒源 有不同的USART/LPUART喚醒源可用於將MCU從低功耗模式喚醒:

- 通過USART/LPUART_CR3寄存器的WUS位欄位選擇的特定事件。 00:在位址匹配時喚醒(按照USART/LPUART_CR2寄存器的ADD[7:0]和ADDM7的定義) 01:保留 10:檢測到Start位時喚醒 11:在每次接收到資料時喚醒(即USART/LPUART_ISR寄存器中RXNE置位) 當喚醒事件得到驗證時,通過硬體將USART/LPUART_ISR寄存器中的WUF標誌置位元,無 論MCU處於低功耗模式還是運行模式。如果USART/LPUART_CR3寄存器中的相應中斷使能位(WUFIE)於置位,它將生成喚醒中斷。

- RXNE中斷 在進入低功耗模式前,必須通過USART/LPUART_CR1寄存器中的RXNEIE位置位來使能 RXNE中斷。 為使USART/LPUART能夠將MCU從低功耗模式喚醒,在進入低功耗模式前, USART/LPUART_CR1控制寄存器中的UESM位必須置位。

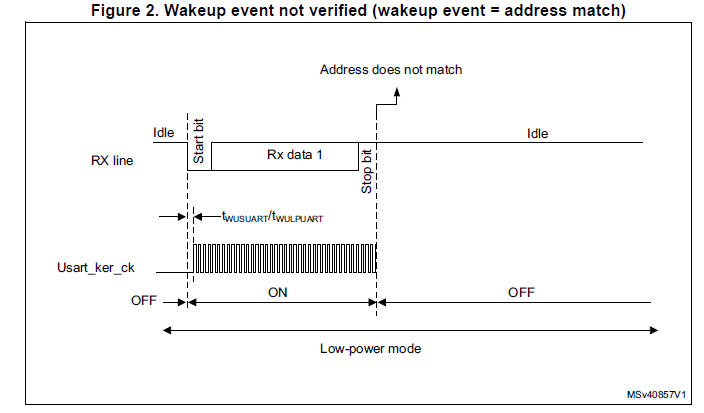

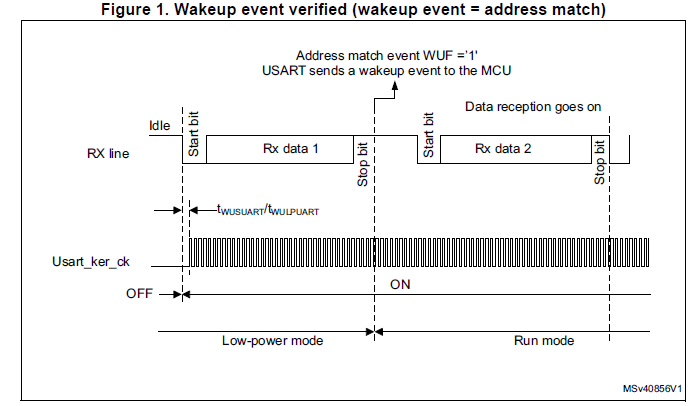

如果STM32 MCU處於低功耗模式且用作USART/LPUART內核時鐘的HSI時鐘關閉,當在 USART/LPUART接收線路上檢測到下降沿時,USART/LPUART介面請求重新開啟HSI時鐘。然後使用HSI時鐘進行幀(frame)接收。 如果喚醒事件得到驗證,將從低功耗模式喚醒MCU並進行正常的資料接收。 如果喚醒事件未得到驗證,HSI時鐘將重新關閉,MCU不喚醒並維持低功耗模式,內核時鐘請求被釋放。圖三和圖四顯示了程式設計為“位址匹配檢測”的喚醒事件的範例。

圖三

圖四

USART接收器容差則取決於下列參數:

– 通過USART_CR1寄存器中的M位元配置的9、10或11位元字元長度

– 通過USART_CR1寄存器中的OVER8位元配置的8倍或16倍過取樣

– USART_BRR寄存器的BRR[3:0]位等於或不等於0000。

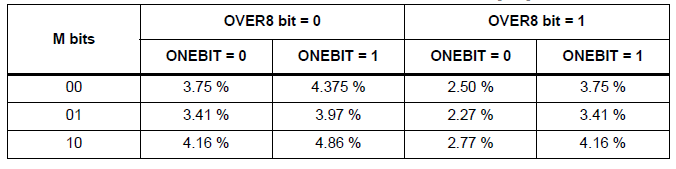

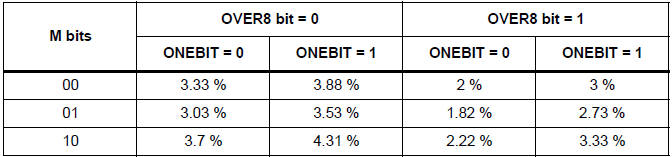

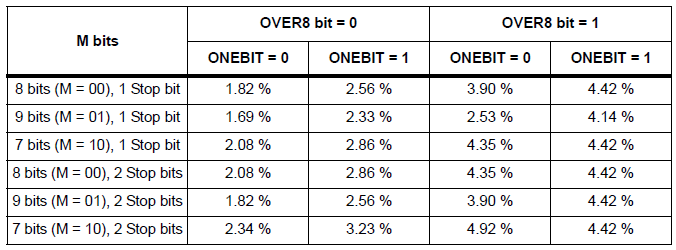

– 根據USART_CR3寄存器中的ONEBIT位,使用一個或三個取樣位元進行資料取樣表一和表二基于上述参数的值总结了USART接收器容差。

表一BRR [3:0] = 0000 時的 USART 接收器容差

表二BRR[3:0] # 0000 時的 USART 接收器容差

LPUART接收器容差則取決於下列參數:

– 通過LPUART_CR2寄存器中的STOP[1:0]位元元配置的停止位元元數。

– LPUART_BRR寄存器值

表三基於上述參數的值總結了USART接收器容差。

表三LPUART接收器的容差

僅當總時鐘系統偏差小於USART/LPUART接收器的容差時,USART/LPUART非同步接收器才能正 常工作。影響總偏差的因素包括:

- DTRA:發送器誤差引起的偏差(其中還包括發送器本地振盪器的偏差)

- DQUANT:接收器的串列傳輸速率量化引起的誤差

- DREC:接收器本地振盪器的偏差

- DTCL:傳輸線路引起的偏差(通常是由於收發器所引起,它可能會在低電平到高電平轉 換時序與高電平到低電平轉換時序之間引入不對稱)

其中,DWU為使用從低功耗模式喚醒時採樣點偏差導致的誤差。 可按以下方式計算允許從低功耗模式正確喚醒的最大串列傳輸速率:

- 以具有9位元資料長度、M位元 = 01的USART/LPUART接收器為例 DWU max = tWUUSART/WULPUART /(11 x Tbit min) 串列傳輸速率最大值 =(11 x DWU max)/ tWUUSART/WULPUART 其中,Tbit Min 是最小位持續時間

- 以具有8位元資料長度、M位元 = 00的USART/LPUART接收器為例 DWU max = tWUUSART/WULPUART /(10 x Tbit min) 串列傳輸速率最大值 =(10 x DWU max)/ tWUUSART/WULPUART

- 以具有7位元資料長度、M位元 = 10的USART/LPUART接收器為例 DWU max = tWUUSART/WULPUART /(9 x Tbit min) 串列傳輸速率最大值 =(9 x DWU max)/ tWUUSART/WULPUART

以OVER8 = 0、M位 = 10、 ONEBIT = 1且BRR [3:0] = 0000的的STM32L4 USART接收器 為例。

在這些條件下,根據表 1:BRR [3:0] = 0000 時的 USART 接收器容差USART 接收器的容差為 4.86 %。

考慮一種理想情況:參數 DTRA、DQUANT、DREC和DTCL為 0%,則DWU最大值為4.86% 。 實際上,我們至少需要考慮HSI不準確性。 假設 HSI 不準確性為 1 %, tWUUSART = 8.5 μs (對於停止模式 1/2) DWU max = 4.86 % - 1 % = 3.86 % Tbit min = 8.5 μs / (9 x 3.86 %) = 24.4 μs。 在這些情況下,允許從低功耗模式正確喚醒的最大串列傳輸速率為 1/23.31 μs = ~ 40 Kbaud。

ST 產品連結

評論