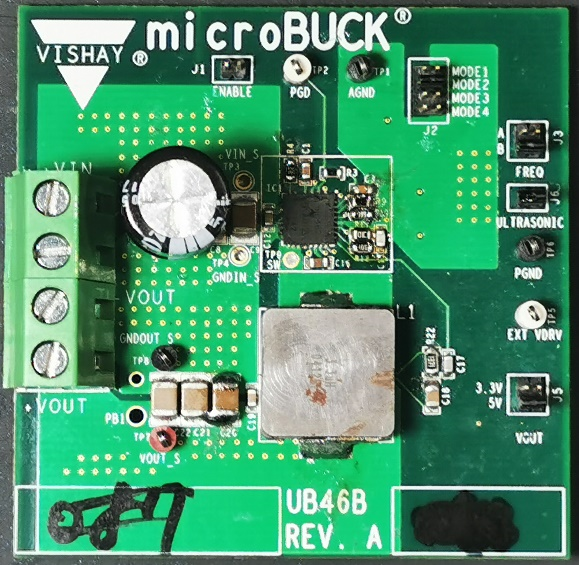

Si46EDB 是 Vishay 推出的一個 Buck Converter,EVM 上可針對各種功能模式以跳線方式來調整,調細可調整的模式如下所示:

J1 : 致能腳位:連接高電位致能,連接低電位禁能。可以連接到 60V。

J2 : 工作模式:

模 式 選 擇

模式 外接電阻 ( KΩ ) 省電模式 內部 VDRV REGULATOR

|

模 式 選 擇 |

|||

|

模式 |

外接電阻 ( KΩ ) |

省電模式 |

內部 VDRV REGULATOR |

|

1 |

0 to 100 |

Enable |

ON |

|

2 |

298 to 304 |

Disable |

ON |

|

3 |

494 to 504 |

Enable |

OFF(1) |

|

4 |

900 to 2200 |

Disable |

OFF(1) |

備註 :

(1) 需接 5V 在 VDRV 接腳 , 而且模式不會在開機後鎖住 , 可以隨時改變模式

J3 : 切換頻率設置。

J4:P1 - +VIN

P2 - PGND

P3 - AGND

P4 - +VOUT

J5:輸出電壓設置,3.3V / 5V 選擇

J6:Ultrasonic 音頻設置

二、詳細規格

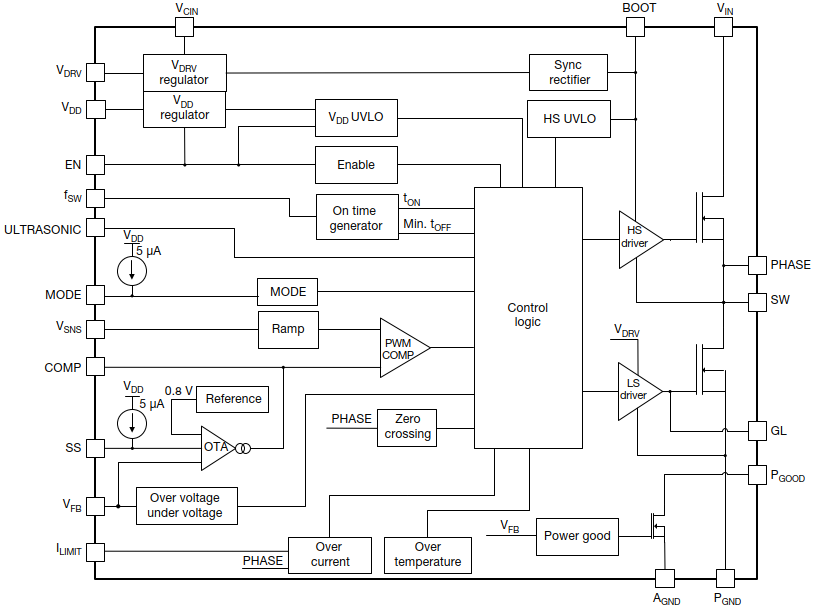

1. 電源拓撲 : 固定導通時間降壓轉換器 ( Constant on-time synchronous buck converter )

2. 輸入電壓範圍 : DC : 4.5V ~ 60V

3. 可調整最低電壓 : 0.8V

4. 最大可輸出電流 :

|

|

Part Number |

輸出電流 ( A ) |

|

1 |

SiC461EVB |

10 A |

|

2 |

SiC462EVB |

6 A |

|

3 |

SiC463EVB |

4 A |

|

4 |

SiC464EVB |

2 A |

5. 工作頻率範圍 : 100KHz ~ 2MHz

6. 最高效率 : 97%

7. 輸出電壓精準度 : ±1% 輸出電壓

8. 音頻模式 ( 超聲波模式 ) :

a. Ultrasonic Pin : 設成 1 , 使芯片最低工作在 20KHz , 避開音頻範圍

b. Ultrasonic Pin : 設成 0 , 芯片將工作低於 20KHz , 可能會有音頻噪聲

9. 保護功能 :

a. 逐波限流 ( cycle by cycle current limit )

b. 過溫保護 ( over temperature protection )

c. 短路保護 ( short circuit protection )

d. 欠壓保護 ( under voltage protection )

e. 過壓保護 ( over voltage protection )

10. 工作溫度 : -40 ~ +125°C

11. 其他優點 :

內含 high / low side MOSFET , 減少外部線路

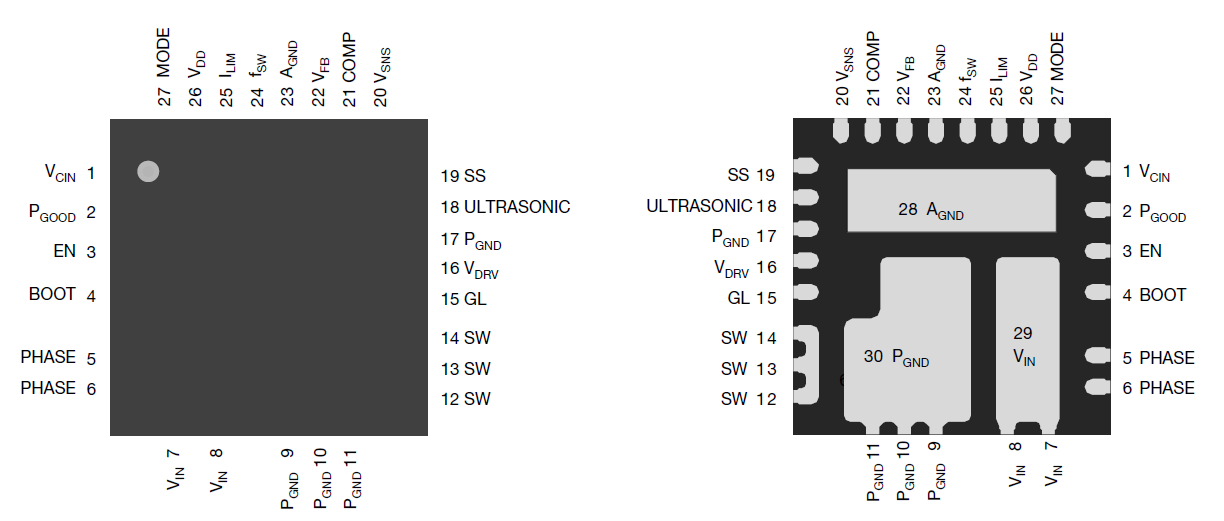

三、包裝及方塊圖

四、腳位功能說明

|

Pin 功能定義 |

||

|

PIN NUMBER |

SYMBOL |

DESCRIPTION |

|

1 |

VCIN |

內部穩壓器 VDD 與 VDRV的供電電壓,需與 VIN 連接,或連接至大於 5V 的較低電壓電源以降低內部穩壓器的損耗。 |

|

2 |

PGOOD |

Open-drain Power Good 指示引腳,高阻抗表示電源良好,需外接上拉電阻。 |

|

3 |

EN |

致能引腳,施加高 / 低電平可以使 IC 致能 / 禁用,可耐壓至 60V。 |

|

4 |

BOOT |

高端閘極驅動器靴帶電路電壓。 |

|

5, 6 |

PHASE |

高端閘極驅動器電流回流路徑。 |

|

7, 8, 29 |

VIN |

電源輸入端,高端 MOSFET 集極。 |

|

9, 10, 11, 17, 30 |

PGND |

電源參考地。 |

|

12, 13, 14 |

SW |

降壓式轉換器的開關切換點。 |

|

15 |

GL |

低端 MOSFET 閘極訊號 |

|

16 |

VDRV |

內部閘極驅動器供電電壓。當使用內部 LDO 供電時,則 VDRV 是 LDO 輸出電壓。連接 4.7 uF 去耦電容至 PGND。 |

|

18 |

ULTRASONIC |

浮接可以禁用 / 連接至 VDD 可以致能超聲波模式。 |

|

19 |

SS |

透過連接一個對AGND的電容設置軟啟動的斜率。 |

|

20 |

VSNS |

功率電感信號反饋功能引腳,用作控制系統補償。 |

|

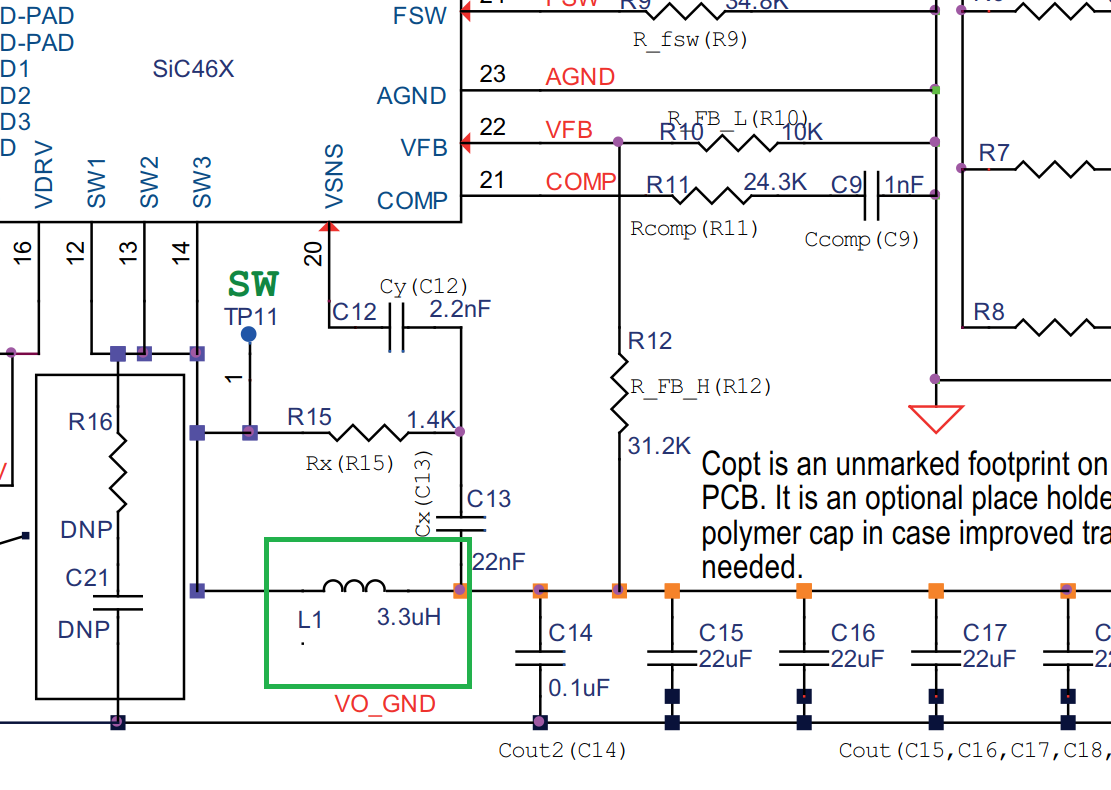

21 |

COMP |

內部誤差放大器輸出。反饋迴路補償器通過引腳連接至AGND。 |

|

22 |

VFB |

開關穩壓器的反饋輸入引腳,用以設置輸出電壓。連接一個由VOUT到AGND的分壓電阻串。 |

|

23, 28 |

AGND |

類比訊號參考地。 |

|

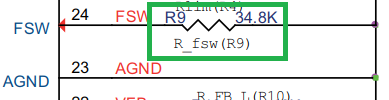

24 |

FSW |

通過連接一個對AGND的電阻來設置脈波的高電平時間。 |

|

25 |

ILIMIT |

通過連接一個對AGND的電阻來設置電流限制。 |

|

26 |

VDD |

IC 的供電電壓。當使用內部 LDO 時,則是 LDO 輸出,連接 1uF 去耦電容至AGND。 |

|

27 |

MODE |

通過連接不同的電阻至AGND來設置不同的工作模式。 |

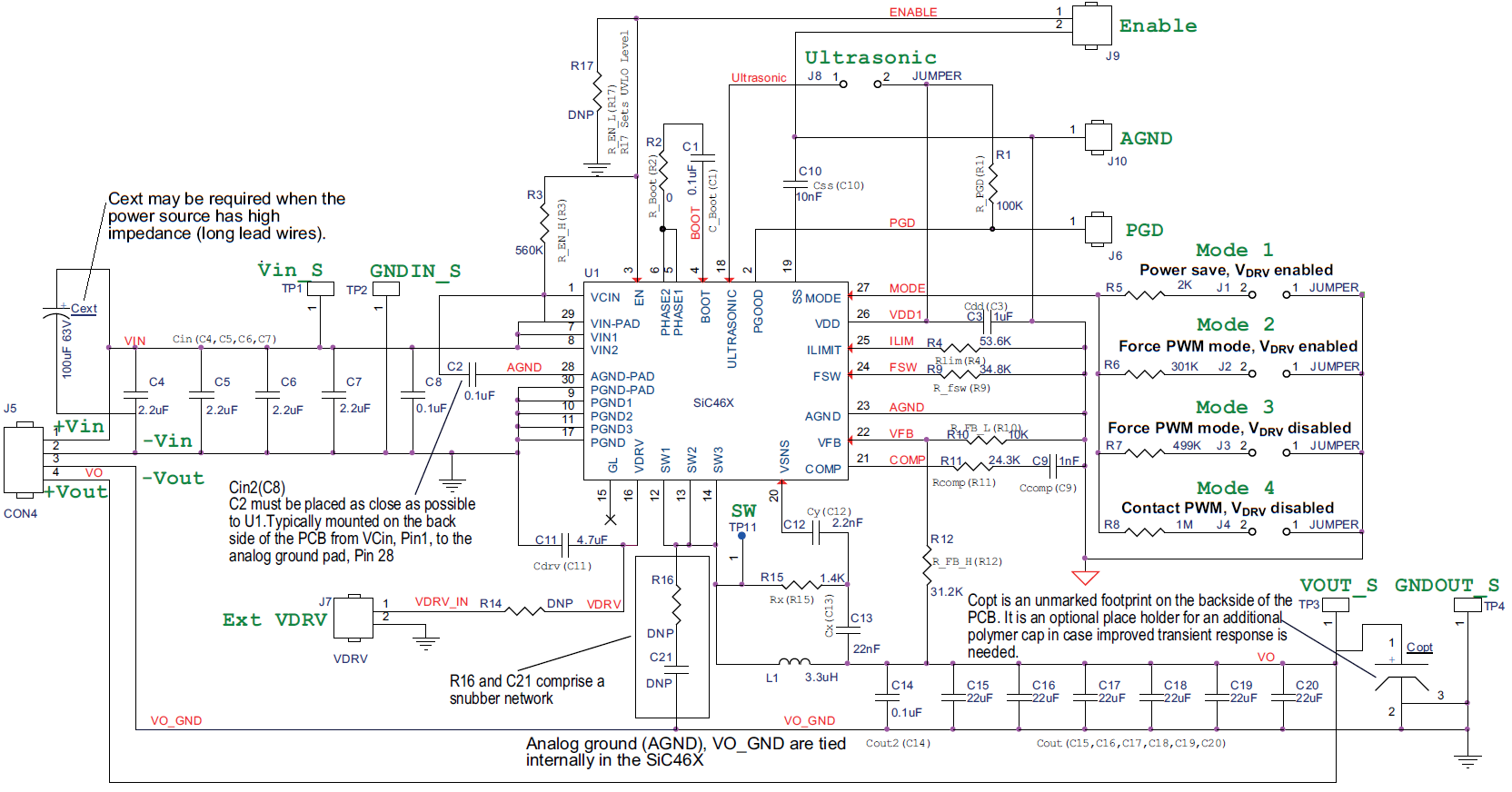

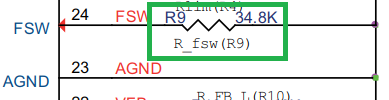

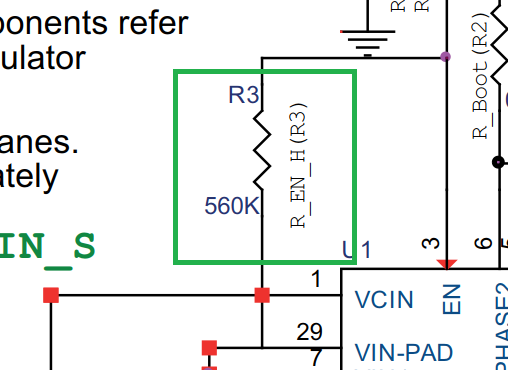

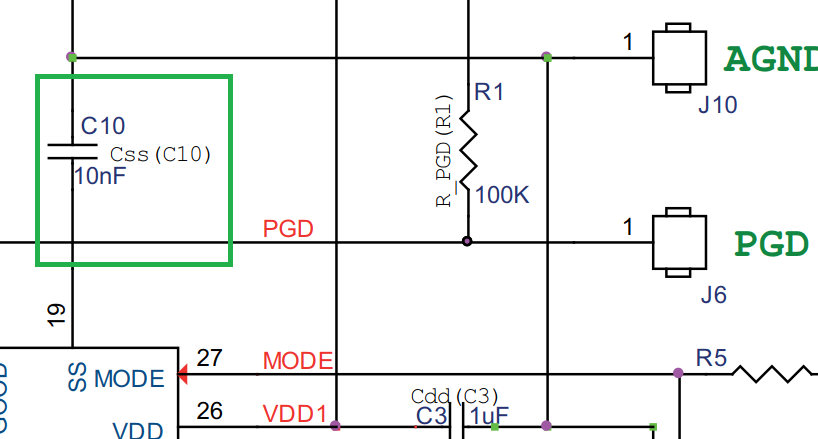

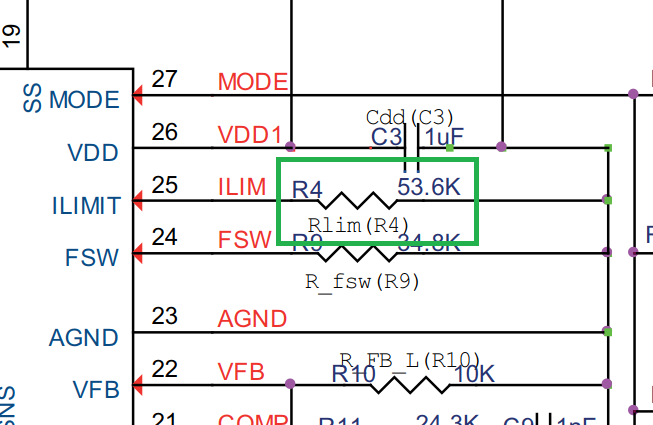

五、線路圖

六、參數設置

1. 設置輸出電壓

通過修改 VFB 連接的分壓電阻可以變更輸出電壓。其電阻計算公式如下,

VFB=0.8 V,R10 的電阻最大只能到 10k,以防止輸出電壓在空載時出現浮動。

R12= ( R10 ( VOUT - VFB ) ) / VFB

整理後,輸出電壓的計算方式如下 :

VOUT = ( R12 × VFB ) / R10 + VFB

若以 EVM 設計,R12=31.2K,取 R10=10K

VOUT = (31200×0.8) / 10000 + 0.8 = 3.296V

2. 決定切換頻率

修改 Rfsw 可以改變頻率。計算公式如下,SiC46x 可以工作在在 100kHz 到 2MHz 之間。

Rfsw = R9 = VOUT / ( Fsw × 190 × 10^(-12) )

整理後,開關頻率的計算方式如下 :

Fsw = VOUT / ( R9 × 190 × 10^(-12) )

以 EVK 設計為例,R_9=34.8K

Fsw =3.3 / ( 34800 × 190 × 10^(-12) ) ≅ 500KHz

3. 電感計算範例

首先由輸出電壓、輸入電壓與頻率計算導通時間。

ton = VOUT / ( Vin_max × Fsw ) = 3.3 / ( 60 × 500000 ) = 110 ns

接著由導通時間計算電感感量,K 是所需的最大輸出電流漣波與輸出電流的的百分

比,通常不超過 30%,但可以依設計需求調整。SiC462 最大電流為 6A,K值則

取 K = 0.3。

L = ( ( VIN - VOUT ) × ton ) / ( Iout_max × K ) = ( ( 60 - 3.3 ) × 110 × 10^(-9) ) / ( 6 × 0.3 ) = 3.465 uH

取接近值,L=3.3 uH。

4. 轉導放大器補償 RC

為了得到高頻寬,需要利用以下公式計算轉導放大器的外部補償,建議的 C_9 值是 1nF, C_OUT 是所有輸出電容的加總。

R_11 = ( L × COUT )^( 0.5 ) / C9 =( 3.3 × 10^( -6 ) × 132.1 × 10^(-6) )^(0.5) / ( 1 × 10^(-9) ) = 20.878K

取值 R11 = 24.3K。

5. 致能引腳電壓

引腳內部有 5MΩ 下地電阻,引腳在電壓超過 1.4V 時使 IC 開始工作。可以輸入一個固定電壓,或透過一個電阻連接到 VIN。

6. 軟啟動設置

軟啟動功能用於限制啟動時的電流大小,透過將 SS 引腳連接至一個積層電容可以簡單實現。開機時 IC 會從 SS 引腳輸出一個恆定電流對電容充電,100nF 電容可以提供大約 16ms 的軟啟動時間,其計算公式如下,建議選用的電容小於 1uF,EVM 選擇的是 10 nF,軟啟動時間計算如下 :

tss = ( Css × 0.8 ) / ( 5 × 10^(-6) ) = ( 10 × 10^(-9) × 0.8 ) / ( 5 × 10^(-6) ) = 1.6 ms

7. 限流電阻

透過在 ILIMIT 間設置的電阻大小可以更改電流限制點,以電流限制在 9.9A,其計算公式如下 :

RILIM = KLIM / ( Iout_max - ( ( VIN - VOUT ) × VOUT ) / ( 2 × fsw × VIN × L ) ) = 480000 / ( 10 - ( ( 60 - 3.3 ) × 3.3 ) / ( 2 × 500000 × 60 × 3.3 ×10^(-6) ) ) = 53009

取電阻值 53.6K 代回 :

Iout_max = ( ( VIN - VOUT ) × VOUT ) / ( 2 × fsw × VIN × L ) + KLIM / RILIM = 9.9 A

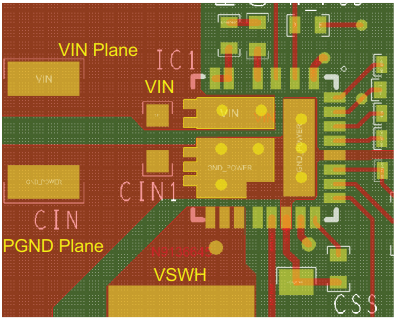

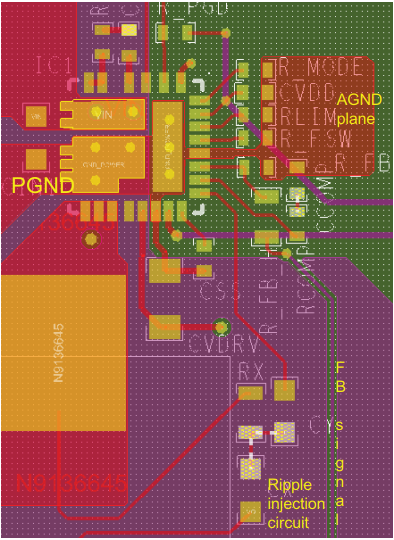

七、LAYOUT 建議

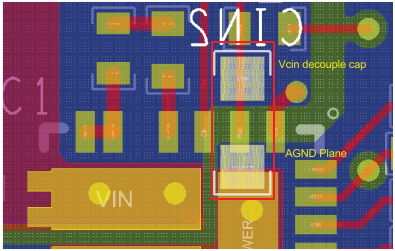

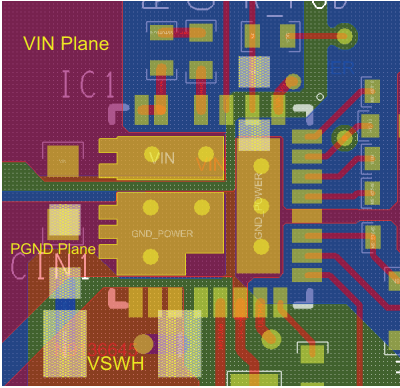

VIN / GND 平面與去耦

- 在 VIN 與 PGND 間應有陶瓷電容相連,並放置在盡可能靠近元件的位置。

- 應搭配使用樹種陶瓷電容的容值與包裝來涵蓋去耦的頻率。

- 容值較小的電容應越靠近 VIN,以提供高頻的響應。

VCIN 引腳

- 同時是內部穩壓器與 tON 控制模塊的輸入引腳,tON 會隨輸入電壓變化,且一定要在靠近 IC 的位置加上去耦電容。

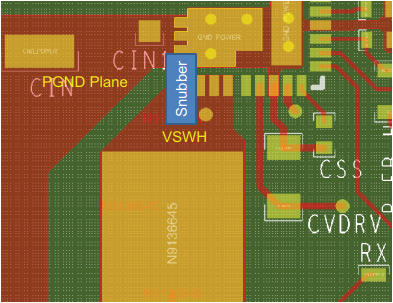

SW 平面

- 使用大面積,低阻抗的舖銅連接電感。若需放置 snubber,則如圖中所示放在 Bottom 面。

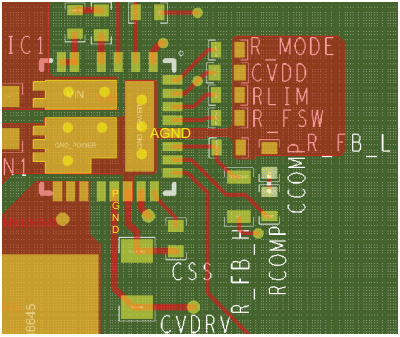

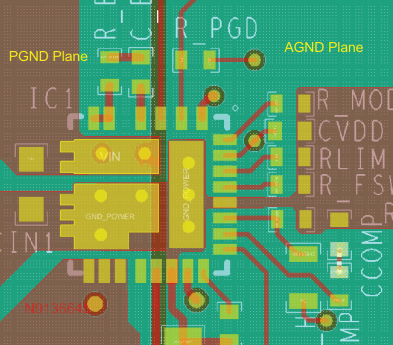

VDD / VDRV 輸入濾波

- CVDD 電容需放在 VDD 與 AGND 之間來過濾雜訊。

- CVDRV 電容需放在靠近 VDRV 與 PGND 引腳的位置,以減少線阻並提供低端 MOSFET 最大的瞬間驅動電流。

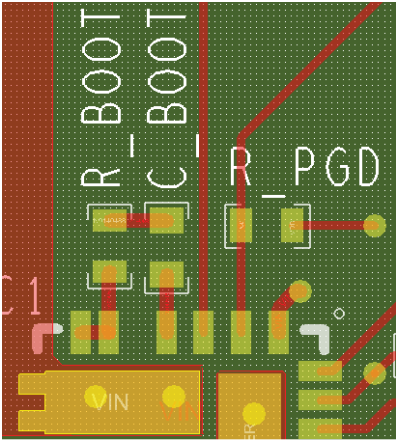

啟動電阻與電容

- CBOOT 與 RBOOT 需放在極靠近 PHASE 與 BOOT 引腳的位置。

- 為降低寄生電感建議使用 0402 封裝的電阻與電容。

訊號走線

- 將類比小訊號與高電流路徑分離。如上圖所示,當控制用的小訊號放在右側時,存在高 dv/dt 與 di/dt 的大電流路徑則放置在元件左側,所有小訊號元件需緊鄰元件放置並最小化走線長度。

- AGND 中的 PIN 23 需要與 PGND 單點連接,將 AGND 鋪銅與 PIN 23 連接可以降低雜訊干擾。

- 反饋訊號可以使用內層走線,且須遠離 SW 並以地平面隔離。

- 漣波注入電路放在電感旁,建議使用 Kelvin connection ( 如上圖所示 )。

增加散熱路徑與複數電源路徑平面

- 可在 VIN 與 PGND 焊點增加散熱貫孔,利用內層來散熱與增加電流路徑。

- 可以增加額外的貫孔在 VIN 與 PGND 平面來改善散熱,並在底層增加 VIN 與地平面鋪銅提高功率承受能力。

- SW 焊點可以視為一個干擾源,而且並不建議使用貫孔

- 理想的貫孔尺寸是 8mil 與 10mil,貫孔可能造成溢錫或其他問題,請諮詢打件廠商。

地平面

- 建議將靠近 Top 層的第一個內層設計為地平面。

- 這個內層提供隔離 Top 層雜訊與內層訊號的作用。

- 內層地可以切開為 PGND 與 AGND

八、參考文獻

SiC46x Datasheet : https://www.vishay.com/docs/65124/sic46x.pdf

評論